#### CHAPTER IV

#### DESIGN OF REGULATOR CIRCUIT

A step by step calulation of circuits elements of an automatic voltage regulator for alternator will be described in the following sections in this chapter. The design is started at the power controller stage and worked backward to the comparison and sensing stages. The required specification of the regulator to be designed are as follows:

> Voltage Regulation : Within ±2.5% from no load to full load and over a range of power factor from 1.0 to 0.8 lagging.

Regulator Output : 25 to 85 VDC at 10 amperes maximum continuous. Voltage Adjust Range at No Load : # 10 %

4.1 Power Controller Stage

Refer to Figure 3.6, A 110 VAC which is taken from the alternator terminals was chosen as the input voltage to the power controller stage. It is most practical to select the values of resistor  $R_{11}$  and capacitor  $C_5$  in the suppression circuit by trial method via an examination of the waveform on an oscilloscope, and practically the value of  $R_{11}$  is in the order of a few hundred ohms and a capacitor  $C_5$  in the order of 0.1 to 0.22 microfarads.

Selection of a 270  $\cap$  for R<sub>11</sub> and 0.1 microfarad for C<sub>5</sub> in this circuit provide a proper suppression. Other components value in the circuit can, however, determined by a straight forward manner.

The rating of components in this circuit are listed below:

| SCR1 and SCR2                    | : | 15 A (rms) | 400 V (\$4015L) |

|----------------------------------|---|------------|-----------------|

| 0 <sub>8</sub> - 0 <sub>12</sub> | : | 10 A (avg) | 200 V           |

| с <sub>5</sub>                   | : | 0.1 JuF    | 400 V           |

| в <sub>11</sub>                  | : | 270 n. 1   | w.              |

#### 4.2 Firing Circuit

In designing the firing circuit the triggering pulse period must be determined first. The period of the free running frequency of UJT is long when the alternator is at no load and becomes shorter when the load on the alternator is increased. The triggering pulse period at these conditions (no load and full load) can be determined as follows.

a) For Alternator at Noload. (Minimum Regulator Output)

Since the specified minimum output voltage of the regulator is 25 VDC, but it is a common practice to design a regulator with a slightly lower output value than that of the specified value, ie. a 20 VDC for this design, in order to ensure satisfactory operation of the circuit. The average voltage from a full wave rectifier circuit is

$$V_{av} = \frac{1}{\sqrt{n}} \int_{\Theta} V_{m} \sin \omega t \, d \, \omega t \, \dots \qquad (4.1)$$

Where \

V : average voltage

- V ; peak or crest voltage of the sine wave

- angular velocity

- $\theta$  : firing angle

The output voltage of the regulator at this no load condition is

$$\begin{aligned}

V_{av} &= 20 \\

&= \frac{1}{4!} \int V_{m} \sin \omega t \, d \, \omega t \\

&= \frac{1}{4!} \int V_{m} \sin \omega t \, d \, \omega t \\

&= \frac{1}{4!} \int 110 \sqrt{2} \sin \omega t \, d \, \omega t \\

&= \frac{1}{4!} \int (-\cos \omega t)^{4!} \\

&= \frac{110 \sqrt{2}}{4!} (-\cos \omega t)^{4!} \\

&= \frac{1}{4!} \int (-\cos \omega t)^{4!} \\$$

The frequency of the generated voltage is 50 Hz , that is each half cycle ( $180^{\circ}$ ) of the sine wave will correspond to a period of time of 10 ms. Then at the firing angle of  $126.6^{\circ}$  will correspond to a period of time of  $\frac{10}{180} \times 126.6 = 7.0$  ms.

It is therefore, at minium regulator cutput voltage, the timing period of the triggering pulse is 7.0 ms.

### b) For Alternator at Full-load (Maximum Regulator Output)

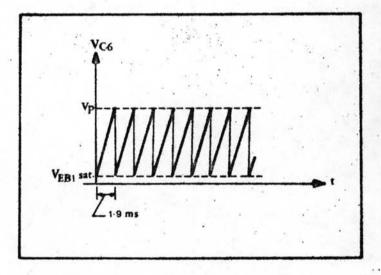

At the maximum regulator output voltage, a slightly higher output value than that of the specified value, ie. a 90 VDC was selected for the design in order to ensure satisfactory operation of the circuit. The triggering pulse period of this condition can be determined in the same way as at the noload condition and this value of time is 1.9 ms.

A 27 VDC was selected for the DC supphy voltage of the circuit. A 2N2646 unijunction transistor was chosen for the firing circuit for it has low peak-point current, low emitter reverse current and easily obtained in local market with a resonable price. The data sheet for the 2N2646 (Appendix A) gives the following specifications.

> $V_{\text{EB1 (sat)}} = 3.5 \text{ V typical } I_p = 5.0 \ \mu\text{A maximum}$   $\gamma = 0.56 - 0.75 \qquad I_v = 4.0 \ \text{mA minimum}$  $r_{\text{BB}} = 4.7 - 9.1 \ \text{Ko} \qquad (\text{Typical 7.0 \ Ko})$

The average value of the intrinsic standoff ratio is

$\gamma_{av} = \frac{0.56 + 0.75}{2} = 0.655$

From eq. 3.3 ; the peak-point voltage is

$V_{p} = V_{D} + \gamma V_{EE}$ = 0.6 + (0.655 × 27) = 18.285 V

And the valley voltage

$$V_v \neq V_{EB1 (sat)}$$

From eq. 3.2

)

$$P_{E}(max) \leq V_{EE} - V_{p}$$

$$I_{p}$$

$$= \frac{27 - 18.285}{5 \mu A}$$

$$= 1.743 M\Omega$$

From eq. 3.4

$$R_{E} (min) \leq \frac{V_{EE} - V_{V}}{I_{V}}$$

= 27 - 3.5

4 mA

= 5.875 KG

It is seen from Figure 3.4 that the output pulse or the oscillation period of the UJT  $Q_3$  is controlled by varying the emitter resistance  $(R_{CE} \text{ of } Q_2)$ , the value of the emitter capacitor  $C_6$  must be determined at the minimum time of pulse period (maximum regulator output voltage) that is at the pulse period of 1.9 mS.

From eq. 3.1

1

$$C_{6} \leq \frac{t (\min)}{R_{E_{min}} \ln\left(\frac{V_{EE} - V_{0}}{V_{EE} - V_{0}}\right)}$$

=  $\frac{1.9 \times 10^{-3}}{5.875 \times 10^{3} \ln\left(\frac{27 - 3.5}{27 - 18.285}\right)}$

= 0.326 /4F

A standard value of 0.22  $\mu$ F 400 V for C<sub>6</sub> was used.

The base 1 resistor  $R_{18}$  can be directly determined from equation 3.5 as follow,

$$R_{18} \stackrel{!}{=} \frac{0.2 r_{BB} (min)}{V_{EE}}$$

$$= \frac{0.2 \times 4.7 \times 10^{3}}{27}$$

$$= 34.82 \Omega$$

A standard value of 33  $n \frac{1}{2}$  W for R<sub>18</sub> was used.

The temperature compensation resistor  $R_{17}$  can be approximately determined by using equation 3.6 as follow,

$$R_{17} = \frac{0.7 r_{BB}}{\gamma V_{EE}} + \frac{(1 - \gamma) R_{1B}}{\gamma}$$

$$= \frac{0.7 \times 7.0 \times 10^{3}}{0.655 \times 27} + \frac{(1 - 0.655) \times 33}{0.655}$$

$$= 324.45 = 0$$

A typical standard value of 330  $\Omega_2^1$  W for  $\Pi_{17}$  was used.

The resistors  $R_{19}$  and  $R_{20}$  presented in the circuit of Figure 3.4 are used to limit the gate current of the thyristors, and their values can be determined as follow.

From the specifications of the SCR1 and SCR2 (S 4015L)

$$I_{GT} (max) = 20 mA at T_{C} 25^{\circ} C$$

$V_{GT} (max) = 1.5 V at T_{C} 25^{\circ} C$

$P_{G} (av) = 0.6 W$

Since

$$P_{G} = I_{G} \times V_{G}$$

$$I_{G} \qquad \frac{P_{G}}{V_{G}}$$

$$= \underbrace{0.6}_{1.5} = 0.40 \text{ A}$$

The peak voltage of the cutput pulse from base 1 of the UJT  $(Q_3)$  is

$$V_{cB1} = V_p - V_v$$

= 18.285 - 3.5 = 14.77 V

Then  $R_{19} = R_{20} = V_{cB1} - V_{G}$

$$I_{G} = \frac{14.79 - 1.5}{0.40} = 33.29 \Omega$$

A typical standard resistor of 33 n  $\frac{1}{2}$  W was used for R<sub>17</sub> and R<sub>20</sub>. A 2N4037 silicon FNP transistors of which specification given hereunder was selected for the transistors Q<sub>1</sub> and Q<sub>2</sub> of Fig 3.4.

$$P_{D} = 1.0 \text{ W}$$

$$T_{J} = 200^{\circ} \text{ C}$$

$$V_{CEO} = 40 \text{ V}$$

$$h_{FE} (\text{min}) = 50$$

$$h_{FE} (\text{max}) = 250 \text{ at } I_{C} 0.15 \text{ A}$$

$$V_{CBO} = 60 \text{ V}$$

$$f_{T} = 60 \text{ MHz}$$

Since, the charge in any capacitor can be written as

$\Delta \mathbf{Q} = \mathbf{C} \Delta \mathbf{V}$

In term of charging current, it well be

$I \Delta t = C \Delta V$ or  $I = \frac{C \Delta V}{\Delta t}$

Since the capacitance of the capacitor C6 is 0.22 / F

Then

=  $V_p - V_{EB1}$  (sat) = 18.285 - 3.5 = 14.785 V

## At maximum regulater output

ΔV

Since, at maximum output voltage from the regulator the time of oscillation period is 1.9 ms (see Fig. 4.1) and this corresponds to a maximum average collector current of the transistor  $Q_2$

Therefore,

$$I_{cQ2_{max}} = \frac{C_6 \Delta V}{\Delta t_{min}}$$

=  $\frac{0.22 \times 10^{-6} \times 14.785}{1.9 \times 10^{-3}}$

$$I_{bQ2_{max}} = \frac{I_{cQ2_{max}}}{h_{FE_{min}}}$$

$$= \frac{1.712 \text{ mA}}{50}$$

$$= 0.034 \text{ mA}$$

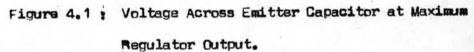

Given the collector voltage of transistor  $Q_1 (V_{c_1})$  to be a half of the dc supply voltage.

In DC amplifier the quiescent voltage must be compensated for in some way in order that the following stage is not saturated and for the circuit of Figure 3.4 the voltage across R13 should be approximately equal to  $V_{CB}$  of transistor  $Q_1^{(7)}$

Since

$$V_{CB_{Q1}} = V_{CE_{Q1}} - V_{BE_{Q1}}$$

and  $V_{CE_{Q1}} = V_{EE} - V_{R14} - V_{z1}$

Select  $V_{z1}$  to be 6.2 volts.

$V_{CB_{Q1}} = V_{EE} - V_{R14} - V_{z1} - V_{BE_{Q1}}$

$= 27 - 13.5 - 6.2 - 0.6$

and

· villing

Then

>

V<sub>R 12</sub>

V<sub>F113</sub>

= 6.7 V=  $V_{\text{EE}} - V_{\text{R}14} - V_{\text{R}13}$ = 27 - 13.5 - 6.7= 6.8 V

It is most practical to design the current through resistors  $R_{12}$  and  $R_{13}$  to such a level that current  $Ib_{Q2}$  will not loaded the divider network.

For this design, a current of 0.6 mA will be chosen for  $I_{A 12}$  which is much more than the current  $Ib_{Q2}$  (0.034 mA)

$$R_{12} = \frac{V_{R12}}{I_{112}}$$

$$= \frac{6.8}{0.6 \text{ mA}}$$

$$= 11.33 \text{ Km}$$

A typical standard value of 12 KO 1 W was used for R 12

$$R_{13} = \frac{V_{P13}}{I_{P13}} \div \frac{V_{P13}}{I_{P12}}$$

$$= \frac{6.7}{0.6 \text{ mA}}$$

$$= 11.17 \text{ Kg}$$

A 12 Kn  $\frac{1}{2}$  W standard resistor for P  $_{13}$  was used.

It can be seen from the characteristics curves of 2N 4037 that the maximum DC forward current gain  $(h_{FE})$  occurs at its collector of about 8 - 12 mA, but high I<sub>C</sub> will consequence in high losses, therefore operating collector current of Q<sub>1</sub> must be chosen at a suitable value near to the current at which maximum h<sub>FE</sub> occurs but with a resonable losses.

In this design, therefore, a minimum collector current of 3 mA is chosen.

Therefore, at maximum regulator cutput;

| I <sub>C</sub> Q1 | -          | I <sub>C</sub> Q1 min                  | = | 3 mA               |

|-------------------|------------|----------------------------------------|---|--------------------|

| I <sub>R 14</sub> | 2          | I <sub>C</sub> Q1 min                  | + | I <sub>13</sub> 13 |

|                   | =          | 3 + 0.6                                |   |                    |

|                   | <b>5</b> . | 3.6 mA                                 |   |                    |

| <sup>H</sup> 14   | =          | V <sub>R 14</sub><br>I <sub>R 14</sub> | • |                    |

|                   | .=         | 13.5<br>3.6 mA                         |   |                    |

|                   | =          | 3.75 Kn                                |   |                    |

# A 3.9 KD $\frac{1}{2}$ W typical standard resistor for R<sub>14</sub> was used

$V_{R16} = V_{EE} - V_{R12} - V_{CB_{Q2}} - V_{p}$ =  $V_{EE} - V_{R12} - (V_{CE_{Q2}} - V_{BE_{Q2}}) - V_{p}$

The minimum collector to emitter voltage of the transistor  $Q_2$  should be more than 1 volt in order to assure that this transistor will never saturated.

V<sub>CE</sub>Q2 min

V<sub>R 15</sub>

Then

>

| = | 27 - | 6.8 | - (1 | - | 0.6) | - | 18,285 |

|---|------|-----|------|---|------|---|--------|

| - | 1,52 | v   |      | 4 |      |   |        |

п<sub>16</sub>

$$= \frac{V_{B 16}}{I_{C_{Q2 max}}}$$

$$= \frac{1.52}{1.712 mA}$$

$$= 0.87 KO$$

= 1 V

A typical standard resistor of 1 Kn 1 W for B 16 was used.

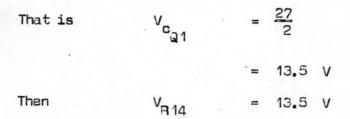

## At minimum regulator cutput

At the output from the regulator is minimum, the time of oscillation period is 7.0 ms (see Fig. 4.2) and this corresponds to a minimum average current of transistor Q2

> Therefore,  $I_{c_{Q2 \text{ min}}} = \frac{C_6 \Delta V}{\Delta t \text{ max}}$  $= 0.22 \times 10^{-6} \times 14.785$ 7.0 × 10^{-3} = 0.465 mA

>

$$Ib_{Q2 \text{ min}} = \frac{I_{C_{Q2 \text{ min}}}}{h_{FE \text{ min}}}$$

$$= \frac{0.465}{50}$$

$$= 0.009 \text{ mA}$$

$$I_{E_{Q2 \text{ min}}} = Ib_{Q2 \text{ min}} + I_{CQ2 \text{ min}}$$

$$= 0.009 + 0.465$$

$$= 0.474 \text{ mA}$$

$$V_{R15} = V_{EE} - V_{R14} - V_{R13} - V_{BE_{Q2}}$$

$$= V_{EE} - (V_{EE} - V_{21} - V_{CE_{Q1} \text{ sat.}}) - V_{R13} - V_{BE_{Q2}}$$

$$= V_{21} + V_{CE_{Q1} \text{ sat.}} - V_{R13} - V_{BE_{Q2}};$$

Since  $I_{R13}$

$$= \frac{V_{R12} + V_{R13}}{R_{12} + R_{13}}$$

$$I_{R13} = \frac{V_{z1} + V_{CE_{Q1} \text{ sat.}}}{R_{12} + R_{13}}$$

$$= \frac{6.2 + 0.3}{12 \text{ K}\Omega + 12 \text{ K}\Omega}$$

$$= 0.271 \text{ mA}$$

Then  $V_{R15}$

$$= 6.2 + 0.3 - (0.271 \times 12) - 0.6$$

$$= 2.64 \text{ V}$$

$$R_{15} \leq \frac{V_{R15}}{I_{E_{Q2} \text{ min.}}} = \frac{2.64}{0.474 \text{ mA}}$$

5.57 KA

4.3 Comparison and Error Amplifier.

A

A 27 VDC was also selected for the supply voltage  $(V_1)$  of the comparison and error amplifier circuit of Fig. 3.3.

The value of the current through the divider network  $R_1$ ,  $R_2$ ,  $R_3$ and  $R_4$  must be much more than the base current of the transistor  $Q_1$  in order that the transistor  $Q_1$  will not loaded the network.

Since  $I_{c_{Q1}} = \frac{V_{EE} - V_{z1} - V_{CE_{Q1}}(sat)}{P_{14}}$

>

Since, the specification of the regulator to be designed specified an allowable voltage adjust range of the alternator terminal voltage to be  $\pm$  10 % of the nominal voltage, then the variable resister R<sub>2</sub> must be designed to fulfill this requirement.

Therefore

$$R_2 = \frac{V_{R2} \max}{I_{R_2}}$$

=  $\frac{0.1 V_1}{I_{R2}} \stackrel{\div}{=} \frac{0.1 V_1}{I_{R1}}$

=  $\frac{0.1 \times 27}{15 m_A}$

= 180  $\Omega$

A standard variable wire-wound resiter of 200  $\Omega$  for R<sub>2</sub> was used.

The variable resistor  $R_3$  was included for providing an additional fine adjustment of the alternator voltage, therefore a 100  $\Omega$  variable wire-wound resistor was selected for  $R_3$

$$V_{R2 \text{ max}} \stackrel{:}{=} V_{z1} + V_{BE_{Q1}} - \frac{1}{2} V_{R2 \text{ max}}$$

$$= 6.2 + 0.6 - \frac{1}{2} (0.1 \times 27)$$

$$= 5.45 \text{ V}$$

$$R1 = \frac{V_{R1}}{I_{R1}}$$

$$= \frac{5.45}{15 \text{ mA}}$$

$$= 363.3 \text{ A}, \text{ Used } 330 \text{ A std. value.}$$

The power dissipated in R<sub>1</sub> is :

V<sub>R1</sub> + ½

>

.....

÷...

$$P_{R_1} = I_{R_1}^2 \times R_1$$

=  $(15 \times 10^{-3})^2 \times 330$

= 0.074 W

A 330 n  $\frac{1}{2}$  W standard resistor for R<sub>1</sub> was used.

$$V_{R_{4}} = V_{1} - V_{R_{1}} - \frac{1}{2} V_{R_{2}} \max$$

= 27 - 5.45 -  $\frac{1}{2} (0.1 \times 27)$

= 20.20 V

$$R_{4} = \frac{V_{R4}}{I_{R4}} \div \frac{V_{R4}}{I_{R1}}$$

=  $\frac{20.20}{15} \max$

1.35 KR, used 1.5 KR std. value.

Power dissipated in R<sub>4</sub> is :

$$F_{R4} = I_{R4}^{2} \times R_{4}$$

= (15 × 10<sup>-3</sup>)<sup>2</sup> × 1.5 × 10<sup>3</sup>

= 0.34 W

A 1.5 Kn 1 W standard resistor for  $R_4$  was used.

The current through resistor  $R_5$  must be much more than the emitter current of  $Q_1$  in order to keep the voltage across zener diode  $z_1$  to a nearly constant value.

| S | R | 7 | R | • | +  |

|---|---|---|---|---|----|

| 4 | 0 |   | 9 | c | ۰. |

>

$$I_{R5} = 15 \text{ mA}$$

$$V_{R5} = V_1 - V_{z1}$$

$$= 27 - 6.2$$

$$= 20.80 \text{ V}$$

$$R_5 = \frac{V_{R5}}{I_{R5}}$$

= 1.39 KA, used 1.5 KA std. value.

The power dissipated in  ${\rm P}_{\rm 5}$  is :

$$P_{R5} = I_{R5}^{2} \times R_{5}$$

=  $(15 \times 10^{-3})^{2} \times 1.5 \times 10^{3}$

= 0.34 W

A 1.5 KQ 1 W standard resistor was chosen for Rg.

Power dissipated in the zener diode z1 is :

$$P_{z1} = I_{z1} \times V_{z1} = I_{R1} \times V_{z1}$$

= (15 × 10<sup>-3</sup>) × 6.2

= 0.073 w

Therefore a BZX 83 C 6V2 zener diode which has a zener voltage of 6.2 volts and rating of 400 mW was chosen for Z1.

4.4 Sensing Circuit

>

A Simple full wave rectifier and L-section LC filter as illustrated in Figure 3.2 was used for the sensing circuit.

Since, the load current of the sensing circuit is  $(I_{R1} + I_{R5})$

$$I_{R1} + I_{R5} = 15 + 15$$

= 30 mA

Then, the load resistance of this circuit is

$$R_{L} = \frac{V_{1}}{I_{R1} + I_{R5}}$$

$$= \frac{27}{30 \text{ mA}}$$

From L-section LC filter, the value of inductance of the filter choke can be determined by (8):

$$L \ge \frac{R_L}{3\omega}$$

Where L : inductance of the filter cheke (Henry)  $\omega$  : angular velocity = 2 ¶ f (Radian)

R : load resistance (Ohm)

f : supply frequency (Hz)

Then

>

$$L_1 \ge \frac{900^{-1}}{3(24 \times 50)}$$

In practical designs, two or three times higher inductance than that calculated value is chosen in order to avoid the saturation of the filter choke. (9)

Therefore, a 3 Henry 100 mA was chosen for L1

Given the ripple of the cutput voltage from the filter to be 2 %, then the value of filter capacitor  $C_1$  can be easily determined as follow.<sup>(8)</sup>

From L-section LC filter,  $r = \frac{\sqrt{2}}{3} \times \frac{1}{2\omega c} \times \frac{1}{2\omega c}$

r : ripple factor Where

$\omega$  : angular velocity = 2  $\pi$  f (radian)

f : supply frequency (Hz)

C : capacitance of the filter capacitor (farad)

L : inductance of the filter choke (henry)

Then

$$0.02 = \frac{\sqrt{2}}{3} \frac{1}{2(2\pi \times 50)C_1} \times \frac{1}{2(2\pi \times 50) \times 3}$$

$C_1 = 19.9 \mu F$

Therefore, a standard capacitor of 22  $\mu$ F/50 WW was chosen for C1

All other remaining components in the sensing circuit can be determined by a straight forward manner. The rating of the components composite in the sensing circuit is listed below

Potential transformer T<sub>1</sub>;

Primary : 0 - 380 V and tapped at 110, 190, 220 volts Secondary : 30 V 100 mA

Diode  $D_1 - D_4$ : 1N4004 Choke  $L_1$ : 3 H 100 mA Capacitor  $C_1$ : 22 /4F 50 WV

#### 4.6 Stabilizing Network

Consider the stabilizing network of Figure 3.7, if  $V_i$  denotes the input voltage to the network and  $V_o$  is the output voltage from the network.

Then the transfer function can be written as equation 4.2

$$\frac{V_{0}(s)}{V_{1}(s)} = \frac{1 + aTS}{1 + TS} \dots (4.2)$$

Where T : time constant =  $(R_9 + R_{10})C_4$

$$R_{3} : \frac{R_{9}}{R_{9} + R_{10}}$$

The technique of improving the response of the system is to choose values of  $C_4$  and  $(R_9 + R_{10})$  so that the time constant T is equal to the time constant of the field winding of the alternator<sup>(6)</sup>. For the conventional alternators of rating in the range considered in this work, ie. 10 - 25 KW, the time constant of the field winding is in the order of 0.2 second.

In this case ;  $(R_9 + R_{10}) C_4 = 0.2$

If a capacitor of  $8 \mu F$  100 V is chosen for C<sub>4</sub>.

$R_{9} + R_{10} = \frac{10.2}{8 \times 10^{-6}}$

Then

The fraction

$a = \frac{R_{10}}{R_{10}}$  is less than unity and  $\frac{R_{10}}{R_{10}}$

if "a" is set to be 0.1

Then

$$\frac{R_9}{R_9 + R_{10}} = 0.1$$

$R_9 = 0.1 (R_9 + R_{10})$

$= 0.1 \times 25$

$= 2.5 \text{ Km}$

A standard resistor of 2.2 Kn  $\frac{1}{2}$  W for  $R_9$  was used.

Substituting  $R_9$  we get ;  $\frac{2.2}{2.2 + R_{10}} = 0.1$

$$R_{10} = 19.8 \text{ K}\Omega$$

A standard value of 22 KA  $\frac{1}{2}$  W for  $P_{10}$  was used.

A resistor of 47 KO  $\frac{1}{2}$ W and a capacitor of  $5\mu$ F 160 V were also chosen for R<sub>8</sub> and C<sub>3</sub> respectively in order to provide a feedback path from the stability network to the error amplifier stage.

The variable resistor  $R_6$  of 2.2 K $\Omega$  was added for providing a further adjust of the feedback current from the R-C stabilizing network to the error amplifier stage input.

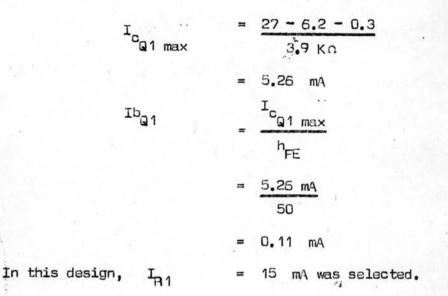

The completed circuit diagram of the voltage regulator for alternator that had just designed is shown in Figure 4.3. The capacitor  $C_7$  of 50 V was provided as a smoothing component to ensure a good DC supply for the error amplifier stage and the diode  $D_7$  prevent the discharge current from  $C_7$  to flow into the firing circuit.

Zener dicde Z used to stabilize the supply bias voltage for the transistor circuits to a nearly constant level. The zener current of the zener dicde  $Z_2$  must be chosen at such a level that has a comparatively larger than its lead current.

Since,  $I_{D7} = I_{EQ1} + I_{R12} + I_{EQ2}$ =  $(3 + \frac{3}{50}) + 0.6 + (1.712 + 0.034)$ = 5.41 mA

Then, choose I72 max = 15 mA

-----

The maximum power disipation of the zener diode  $Z_2$  is :

$$P_{Z2} = I_{Z2} \times V_{Z2}$$

= 15 mA × 27 V

= 0.41 W

A 27 V 1 W zener diode for  $Z_2$  was used.

The resistor R<sub>21</sub> used to reduce the supply voltage to a suitable level for supplying the transistor circuits, and this resistance value can be calculated as follow.

$$R_{21} = \frac{\frac{V_{R21}}{I_{R21}}}{\frac{(110/1.11) - V_{Z2}}{I_{Z2} \max}}$$

$$= \frac{(110/1.11) - 27}{15 m_{A}}$$

$$= 4.81 \text{ KO}, \text{ used } 4.7 \text{ KO std. value.}$$

The power dissipated in R<sub>21</sub> is

$$P_{R21} = I_{R21}^{2} \times R_{21}$$

$$= (15 \times 10^{-3})^{2} \times 4.7 \times 10^{3}$$

$$= 1.06 \quad W$$

A 4.7 Kn 5 W resistor for  ${\rm R}_{21}$  was used.

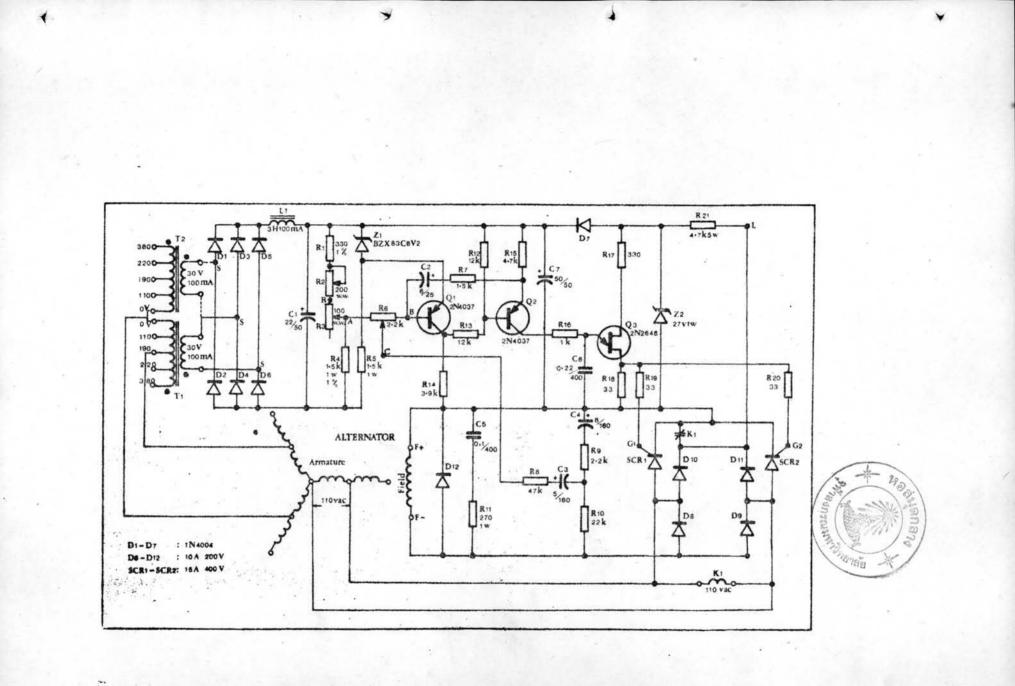

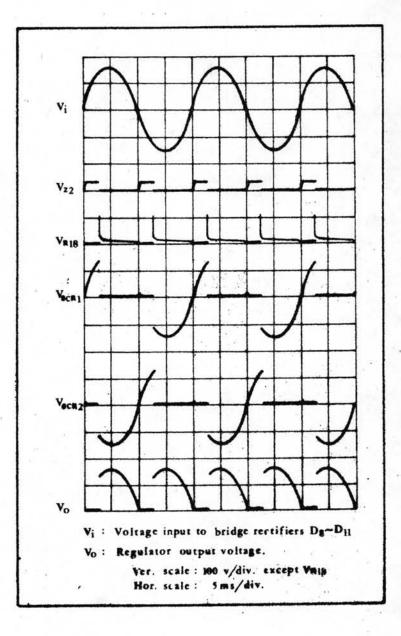

The resistor  $R_7$  of 1.5 K  $\Omega$  and the capacitor  $C_2$  of 6  $\mu$ F/25V had been added in the circuit of Fig. 4.3 to prevent high-frequency instability. The waveform at various parts on the completed circuit of Fig. 4.3 traced on an oscilloscope, by supply a 50 Hz sinusoidal voltage to the power input terminals of the regulator, are illustrated in Figure 4.4 and 4.5.

>

>

Figure 4.3 : Complete Circuit Diagram of the Voltage Regulator for Alternator.

>

7

## Figure 4.4 : Voltage Waveforms at Minimum Specified

Regulator Output Voltage.

>

>

Figure 4.5 : Voltage Waveforms at Maximum Specified Regulator Output Voltage.