#### CHAPTER III

#### CIRCUIT DESIGN

3.1 COMPARATOR DESIGN [5]

The design is divided into three parts :

- Biasing.

- Reference Level.

- Hysteresis Level.

3.1.1 Biasing Design

Given : Positive supply +12 volts, negative supply - 12 volts.

Design Procedure :

Choose pA 710c as the comparator which has the following characteristics :

> Max. positive supply voltage + 14.0 volts. Max. negative supply voltage - 7.0 volts. Differential input voltage ± 5.0 volts. Input bias current 40.0 pA

|               | Mi            | n. Typ  | • Max.  |

|---------------|---------------|---------|---------|

| Positive out  | put level 2.  | 5 V 3.2 | v 4.0 v |

| Negative out  | put level -1. | ov -0.5 | v 0.0 v |

| Positive supp | oly current   | 5.2     | mA      |

| Negative supp | ly current    | 4.6     | mA      |

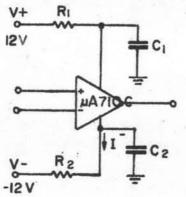

FIG.3.1 Circuit for Determination of R1 and R2.

1

\*

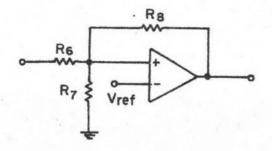

FIG.3.3 Equivalent Circuit for Reference Level Design.

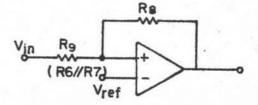

Equivalent Circuit for Hysteresis Design.

Due to the limitation in negative supply requirement i.e. -7 V(Max) at the negative input of the comparator,  $R_2$  must be chosen to drop the excess voltage that is available from the NIM Bin. The value of  $R_2$  can be calculated as follows :

$$I = R_2(Max.) \gg V - 7$$

$R_2(Max.) \gg \frac{V - 7}{I^-}$

$\gg \frac{12 - 7}{h 6} \gg 1.1 \text{ K}\Omega$

Allow  $\pm 5\%$  tolerence, the conventional value of R<sub>2</sub> should be 1.3 K  $\cap$ .

When the comparator is switching from high to low or vice versa a sharp spike may be introduced into the supply line. This can be eliminated using RC filter. To obtain low impedance path for the spike  $C_1$  and  $C_2$  should be in the order of .01  $\mu$ F and be of ceramic type. In order not to lower voltage at the positive supply of the comparator the value of  $R_1$  should be around 100  $\Omega$ .

#### 3.1.2 Hysteresis Level Design

Given Max. input voltage + 10 volts.

Input impedance 1.0 K n.

Peak noise voltage imposes on the input signal

<15 mV.

Design Procedure :

Requirements in input signal and input impedance imply that the max. voltage drop across  $R_7$  should be equal to or less than 5 volts and  $R_6$  plus  $R_7$  should be in the vicinity of 1 K $\Omega$ . Hence for  $R_6 = R_7 = 511 n \pm 1\%$  the above condition will be satisfied.

$R_8$  can now be calculated under the restriction that the hysteresis level under maximum and minimum output voltage be less than 50 mV and greater than 15 mV respectively.

$$\begin{array}{l} v_{o \ \text{High} \ (\text{Min.}) \ (\frac{R_{9}}{R_{8}}) > 15 \ \text{mV} \ \text{and} \ v_{o \ \text{High} \ (\text{Max.}) \ (\frac{R_{9}}{R_{8}}) < 50 \ \text{mV} } \\ \end{array} \\ \begin{array}{l} \text{Hence} & \frac{V_{o \ \text{High} \ (\text{Max.}) \ R_{9}}{50 \ \text{mV}} R_{9} < R_{8} < \frac{V_{o \ \text{High} \ (\text{Min.}) \ R_{9}}{15 \ \text{mV}} \\ \end{array} \\ \begin{array}{l} \frac{2500 \ x \ 505}{50} < R_{8} < \frac{4000}{15} * 505 \\ \end{array} \\ \begin{array}{l} 40 \ \text{K} \ < R_{8} \le 83.3 \ \text{K} \end{array}$$

Choose  $R_8 = 75.5 \text{ Kn} \pm 5\%$

$$\begin{array}{rcl} \text{In I} & = & \text{V}_{\text{ref.}} \left( \frac{R_9 + R_8}{R_8} \right) \\ & & & \text{V}_{\text{ref.}} & \left( R_8 \right) > R_9 \end{array}$$

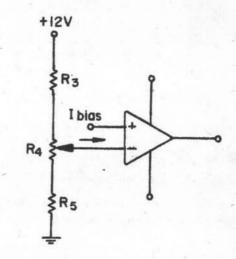

3.1.3 Reference Level Design

Given : Lowest reference level = 50 mV

Highest reference level = 5 volts Design Procedure :

The design should begin with the standard value of  $R_4$ . The value is chosen such that current in  $R_4$  is much greater than  $I_{bias}$  of the comparator. With the wiper sets at its highest and lowest extremes the voltage should be 5.0 volts and 50 mV respectively. Therefore, the current in  $R_h$  is :

$$I_{R4} = \frac{5-0.05}{R_4} = \frac{5-0.05}{1K} = 4.95 \text{ mA} > 100 \text{ I}_{\text{bias}}$$

And also 4.95 mA flows through  $R_3$  and  $R_5$ , hence :

$R_3 = \frac{12-5}{4.95} = 1.42$  K.C.

and  $R_5 = \frac{0.05}{4.95} = 10.1 \Omega$

Let  $R_3$  be 1.42 K  $f_1 \pm 1\%$  and  $R_5$  be  $10 f_1 \pm 1\%$

# 3.2 DESIGN OF TTL DRIVER [6], [7]

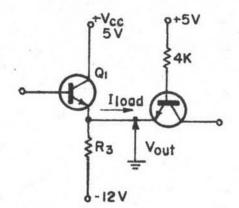

The emitter follower stage acts as an impedance transformers from output to input terminals and is often used as a buffer element between an input and output stage. The driver for the TTL is shown in Fig. 3.4, and the values of  $R_1$ ,  $R_2$  and  $R_3$  must be determined to meet the following specification :

1. For  $V_{in} \leq 1.5 V$ ,  $V_{out}$  should be equal to or less than the logical O input voltage of TTL (i.e.  $\leq 0.8 V$ ).

2. For  $V_{in} > 3 V$ ,  $V_{out}$  should be equal to or greater than the logical 1 input voltage of TTL (i.e >, 2.0 V).

3. Open circuit input causes Vout to approach  $V_{\rm cc}$  .

4.  $V_{bb} = 12 V$ ,  $V_{cc} = 5 V$ .,  $V_{ee} = -12 V$ .

3.2.1 Determination of R

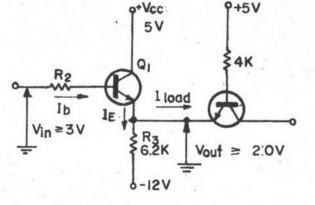

In determining  $R_3$  the worst case occurs when  $R_3$  has to sink the maximum load current, i.e. when Vin is at its lowest maximum voltage and in this case  $V_{in}(Mix.) \approx 0$  volt. Hence  $R_3$ must be small enough to pass at least the current from the input of TTL. The equivalent circuit for calculating  $R_3$  can be drawn as shown in Fig. 3.5.

ADANADA

13TH SIGN

FIG. 3.4 Emitter-Follower Driving one TTL Load.

FIG.3.5 Equivalent Circuit for Determining R<sub>3</sub>.

FIG.3.6 Equivalent Circuit for Determining R<sub>2</sub>.

FIG. 3.7 Equivalent Circuit for Determining R1.

Assume Q<sub>1</sub> be a silicon transistor with  $V_{BE}(ON) = 0.7 V$ , at this instant V<sub>out</sub> should be approximately 0 volt with respect to ground. I<sub>load</sub> is found to be 1.6 mA inward and the value of R<sub>3</sub> is found to be:

$$R_3 \leq V_{ee}$$

$I_{load}$

$\langle \frac{1.2}{1.6 \text{ mA}}$

$\langle 7.5 \text{ K}$

Let R3 be 6.2 KQ ± 5%

Under worst case design one can realized that for  $V_{\rm in} \leq 1.5 v$ ,  $V_{\rm out} \leq 0.8 v$  and hence satisfies the first criterion.

### 3.2.2. Determination of Ro

With the aid of Fig. 3.6 and the second restriction  $(V_{out} \ge 2.0 \text{ V for } V_{in} \ge 3 \text{ V})$ , R<sub>2</sub> must be designed to supply enough base current to drive the required emitter current. For 24 V<sub>out</sub> 45 V, I<sub>out</sub> varies from 40  $\mu$ A to 1mA outwards. Max. emitter current is then found to be

$$I_{E}(Max.) = \frac{V_{out} + V_{ee}}{R_{3}} + I_{load}$$

$$= \frac{12 + 2}{6.2K} + 1 \text{ mA}$$

$$= 3.36 \text{ mA}$$

$$I_{B}(Max.) = \frac{3.36}{h_{rm}} (Min.)$$

Apply Kirchoff's voltage law at the input of the emitter

follower

$$V_{in} - I_{BR_2} - V_{BE}(ON) - V_{out} = 0$$

$$R_2 = \frac{V_{in} - V_{BE}(ON) - V_{out}}{I_C} \cdot h_{FE}(Min)$$

Assume h<sub>FE</sub>(Min) > 50, R<sub>2</sub> is found to be

$$R_2 < (3 - 0.7 - 2) \times 50$$

3.36

$$\langle \frac{0.3 \times 50}{3.36} < 1.5 \text{ K}$$

choose

R2 < 1 K 1 ± 5%

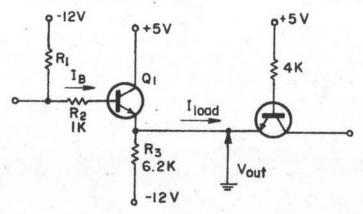

## 3.2.3 Determination of R1

$R_1$  is to be designed such that when the input is held open, the emitter-follower then saturates. The equivalent circuit for calculating  $R_1$  is showr in Fig. 3.7. Under this condition  $R_1$ and  $R_2$  must be small enough to pass excess base current to drive both the sink currents in  $R_3$  and load. Hence  $R_1$  can be calculated from the following expressions:

$V_{bb} - I_B (R_1 + R_2) - V_{BE}(Sat.) - V_{out} = 0$   $(R_1 + R_2) = h_{FE} (Sat.) \left[ V_{bb} - V_{BE}(Sat.) - V_{out} \right] / I_C$ Where I<sub>C</sub> is given by I<sub>C</sub> =  $\frac{V_{out} + V_{ee}}{R_3} + I_{load}$   $= \frac{5 + 12}{6.2 \text{ K}} + 1.6 \text{ mA} = 4.34 \text{ mA}$

Iload is found to be 1.6 mA outward for  $V_{out} = 5V$  and under saturation  $h_{FE}(Sat.)$  usually be much smaller than  $h_{FE}(Min.)$  when the transitor operates in active region in; assume  $h_{FE}(Sat.) = 30$ Then  $R_1 - R_2 \approx 30$ .  $(12 - 0.7 - 5) \approx 43 \text{ K}\Omega$ Let  $R_1$  be 33 K $\Omega \pm 5\%$

### 3.2.4 Determination of the Transistor

Since max. dissipation on transistor never exceeds 25 mW Any type of switching transistor that can withstand the following requirements :

1. Power dissipation of 25 mW.

2. Collector emitter breakdown exceed 5 V.

3. Supply base current > 150 µA and emitter current > 5 mA.

4. Having min.  $h_{\rm FE}$  in active region  $\gtrsim 50$  and min.  $h_{\rm FE}$  under saturation  $\gtrsim 30$  .

can be used and the transitor is found to be 2N6531.

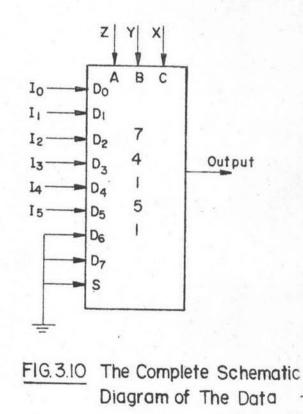

3.3 DESIGN OF MULTIPLEXER TO MECHANIZE LOGIC FUNCTIONS USING MSI [8]

Digital Multiplexer is sometimes called a selector switch. Its function is to select one of the inputs to appear at the output. Knowing standard MSI circuit well one can implement some logic equations with much more intelligently at the system level.

Requirements : A portion of a present time unit is to be required with the followings specification.

1. The portion is to be designed to receive 6 inputs  $I_0 \dots I_5$ which represent the time intervals of 0.1 to 10 sec.(min.)

2. The output of the portion can be selected from only one of the inputs at a time by a group of command in binary code.

Design : Using positive level logic as command. Since 6 inputs are to be transferred to the output one at a time at least 3 bits of binary command must be employed. Let it be designated as X, Y and Z. Fig. 3.8 lists the inputs and outputs correspondences.

| XY | 0   | 1              |

|----|-----|----------------|

| 00 | I o | I <sub>1</sub> |

| 01 | I 2 | Iз             |

| 11 | x   | x              |

| 10 | 14  | 15             |

| СВ | 00             | 01 | 11 | 10             |

|----|----------------|----|----|----------------|

| 00 | Do             | L  | L  | D              |

| 01 | D2             | L  | L  | D <sub>3</sub> |

| 11 | D <sub>6</sub> | .L | L  | D7             |

| 10 | D4             | L  | L  | D5             |

|         | Inputs |        |      |     |

|---------|--------|--------|------|-----|

| Command |        | Output |      |     |

| х       | Y      | Z      | Data | II  |

| 0       | 0      | 0      | Io   | Io  |

| 0       | 0      | 1      | I,   | I I |

| 0       | 1      | 0      | I2   | I2  |

| 0       | 1      | 1      | I3   | 13  |

| 1       | 0      | 0      | 14   | 14  |

| 1       | 0      | 1      | 15   | 15  |

FIG.3.8 Input Output Behavior of Function Under Designed.

|   | Inputs |   |        |                |  |

|---|--------|---|--------|----------------|--|

|   | Select |   | Strobe | Output         |  |

| С | В      | А | S      | Y              |  |

| х | x      | х | н      | L              |  |

| L | L      | L | L      | Do             |  |

| L | L      | н | L      | D              |  |

| L | н      | L | L      | . D2           |  |

| L | н      | н | L      | D <sub>3</sub> |  |

| н | L      | L | L      | D4             |  |

| н | L      | н | · L.   | D5             |  |

| н | н      | L | L      | D6             |  |

| Н | н      | н | L      | D7             |  |

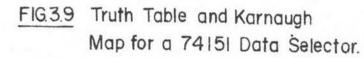

Selection Under Design

Fig. 3.8 shows that the function of this portion is simply a data selector or multiplexer. Select a conventional data selector at hand having at least 3 input commands and 6 data inputs. The device is found to be SN74151 with the following characteristics as shown in Fig 3.9. Compare Fig. 3.8 with Fig. 3.9 with strobe input shorted to ground one can conclude that:

1. X = C, Y = B, Z = A

2.  $I_0 = D_0$ ,  $I_1 = D_1$ ,  $I_2 = D_2$ ,  $I_3 = D_3$ ,  $I_4 = D_4$ ,  $I_5 = D_5$ 3. Unuse data  $D_6$  and  $D_7$  can be either connected to ground or supply since it cannot occur.

4. The input command can be implemented with any thumb wheel switch operated in BCD code with a lock at position 6. Fig. 3.10 concludes all the above results.

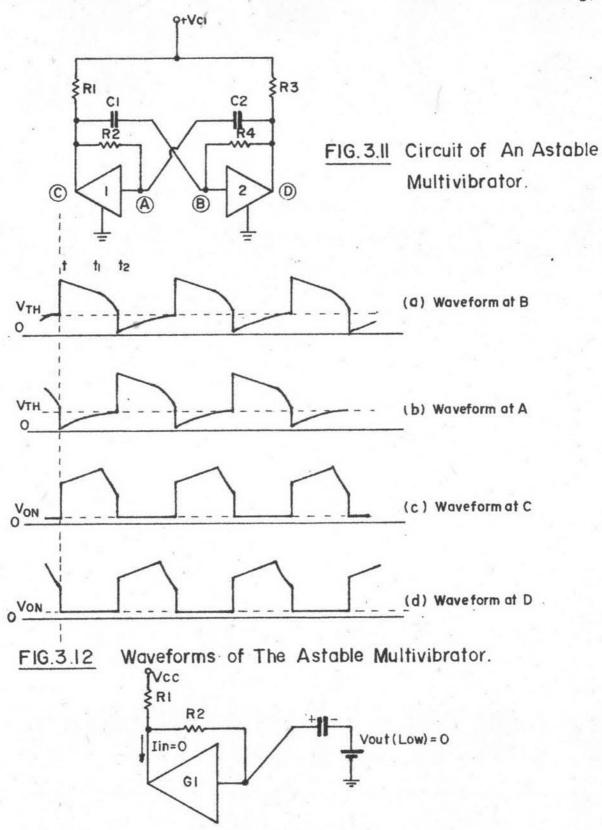

3.4 DESIGN OF ASTABLE MULTIVIBRATOR (9]

The circuit diagram for a free-running multivibrator using two inverter gates is shown in Fig. 3.11. Since capacitive coupling is used between stages, neither gate can remain permanently OFF. Instead, the circuit has two quasi-stable states, and it makes periodic transitions between these states

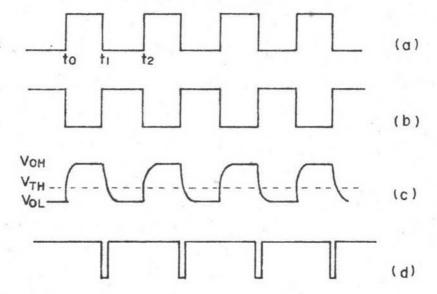

The waveforms at the inputs and outputs of the multivibrator are also shown in Fig. 3.12. Consider that immediately before  $t=t_0$ gate  $G_1$  is in saturation while gate  $G_2$  is OFF. Hence for  $t < t_0$  the output of the gate  $G_1 V_{out}$  (Low ),  $G_2$  is off. Capacitor  $C_1$  charges through  $R_3$  and  $R_4$  towards  $V_{cc}$  causing an exponential rise at point B, waveforms of which is shown by Fig. 3.12a, and when the rise at B

FIG. 3.13 Equivalent Circuit for Calculating The Period of Oscillation.

37

nearly  $V_{TH}$  (the threshold level of the gate  $G_2$ ), gate  $G_2$  starts to conduct. Capacitor  $C_2$  then discharges through the output of gate  $G_2$ , hence an exponential decay is observed at the gate  $G_2$  output (shown by Fig. 3.11d). At  $t = t_0$ , the voltage at B just rises beyond  $V_{TH}$ , immediately the gate  $G_2$  is switched ON. Sudden transition to the ON state of the gate  $G_2$  causes a sharp drop at A, turning the gate  $G_1$  OFF (Fig. 3.11b). The step rise at the output of the gate  $G_1$  depends on  $R_1$ ,  $R_2$ ,  $C_2$  and  $C_1$   $R_4$ , and after the step rise ( $t_0$ )  $C_1$  still gains furthen charges and voltage at C rises towards Vcc. At the instant after the step rise  $C_2$  also charges through  $R_1$ and  $R_2$  until  $t_{\mp}$   $t_1$  the voltage at A reaches  $V_{TH}$  of the gate  $C_1$ (Fig. 3.11a) gate  $G_1$  starts to conducts and after it passes through the threshold level of the gate  $G_1$ , gate  $G_1$  is switched OFF (Fig. 3.11c). And after that the cycle repeats itself.

### 3.4.1 Timing Considerations

The time for each gate to make transition depends on the time required by  $C_1$  and  $C_2$  to charge to the threshold level of the gates and is approximately given by:

$v_c = v_f + (v_i - v_f) e^{-t/RC}$

where

$v_c$  = the voltages on  $C_1$  and  $C_2$  at any instant.

$v_i = initial voltage on C_1 and C_2 at time t = t_0$  $v_f = final voltage on C_1 and C_2 if it is allowed to charge for infinite time.$

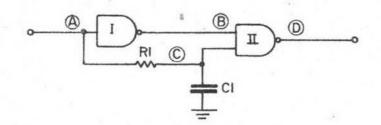

R = resistance in the charging path for  $C_1$  or  $C_2$ . Considering either gate when is in the OFF state suppose gate 1 OFF one can draw an equivalent circuit as shown in Fig. 3.12

38

Hence

$$R = R_1 + R_2$$

$$C = C_2$$

$$V_1 \approx 0$$

$$V_f = V_{cc}$$

For  $t = T_1, v_c = V_{TH}$ , hence

$$v_{\rm TH} = v_{\rm cc} + (0 - v_{\rm cc}) e^{-T_1/(R_1 + R_2)C_2}$$

$$T_1 = (R_1 + R_2)C_2 \ln \left(\frac{1}{1 - V_{\rm TH}/V_{\rm cc}}\right)$$

For symmetrical circuit  $(R_1 + R_2) = (R_3 + R_4)$  and  $C_1 = C_2$  $T = period = 2(R_1 + R_2)C_1 ln (\frac{1}{1 - V_{TH/}V_{cc}})$

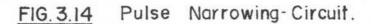

3.5 DESIGN OF PULSE NARROWING CIRCUIT [9], [10]

Often, the controlling input signals received by a sequential system are not in pulse form. In this case, they must be converted into pulse form, usually by a special pulse-narrowing circuit called a pulse generator. The pulse generator circuit responds to changes in its input signal rather than to the logical value of its input. This type of input is said to be transition sensitive, or edge-coupled, indicating its sensitivity to changes in logical value.

The pulse-narrowing action of the pulse generater can be achieved in a variety of ways. In TTL and DTL digital circuits, a resistance-capacitance (R-C) differentiative circuit is often used to generate such a pulse. The diagramand characteristics of such a circuit are shown in Fig. 3.14 and 3.15.

FIG.3.15 a) Waveform at The Input of The Pulse Narrowing Circuit b) Waveform at B is The Invert of A

c) Waveform at A is Delayed by an R-C Circuit at C.

d) Waveform at D the Differentiator Output.

The width of the output pulses can be found as follow :

Prior to  $t = t_1$  voltage at the input of the circuit (at A) is High. Voltage at B is the inversion that of A, hence it must be Low. If the width of the input pulse is long enough for  $B_1 C_1$  to charge to its final value which is usually be the case, then potential at C must be equal to  $V_{OH}$ , the high level of the input voltage. The output of the circuit is BC, hence it must be High and approximately equal to  $V_{OH}$ . At  $t = t_1$  the input makes an abrupt transition from High to Low causes the voltage at B to change to the High state, C then discharges from  $V_{OH}$  to  $V_{OL}$ . At this instant the output then jump from High to Low and remains Low until voltage at C decays passing the gate threshold level( $V_{TH}$ ), it then switch High again and remain in this state until the input make another transition to Low again.

The width of the output pulse can be found from the equation below :

$$v_{g} = v_{f} + (v_{i} - v_{f}) e^{-t/R_{1}C_{1}}$$

where  $v_c = voltage$  on capacitor  $C_1$  at the discharge instant

$v_{f}$  = the final voltage that C<sub>1</sub> must discharge to, and in this case = V<sub>1</sub>

$\mathbf{v}_{i}$  = initial voltage on capacitor C before discharge begins and again in this case =  $V_{OH}$ icr t = T = pulse width of the output and for small value of R  $\approx 220 \Omega$

$$V_{TH} \approx V_{OL} + (V_{OH} - V_{OL}) e^{-T/R_1C_1}$$

$$T \approx R_1C_1 \ln \left(\frac{V_{OH} - V_{OL}}{V_{TH} - V_{OL}}\right)$$

41