#### CHAPTER II

#### TIMER/COUNTER

#### 2.1 GENERAL DESCRIPTION [3]

The Timer-Counter(T.C.) under development is a generalpurpose 6-decade unit that includes a presision preset timing

circuit. It can be used in either a simple or a complex counting

system to control the duration of a counting interval for all the

Counters in the system. When it is operated as a Counter, it

accepts and counts NIM-standard slow positive pulse. Timing

intervals can be set at 0.1 sec. and 0.1 min. steps and will not be

displayed. Only counting data can be printed together with the

counting data from any other ORTEC printing modules by an ORTEC

777 Line Printer or, through ar ORTEC 432A Printout Control, or

by an ORTEC 222, which is a modified Teletype.

The unit is designed for preset timing control of a counting system that includes only one Counter or up to as many as 50 Counters. The associated signals through the rear pannel of the Timer Counter permit a flexible overall system control to be designed for a wide variety of associated system accessories.

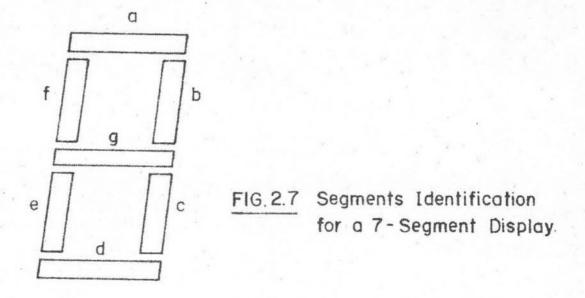

The T.C. is packaged in a MIM-standard double-width module. It includes all the connectors and controls that will be used for either manual or automatic operation and indicates the

accumulated count with 7-segment light-emitting diodes (IED) in a direct-reading display. A start indicator which is also an LED, lights to show when the T.C. is in a counting condition. The start is controlled by the manual Count/Stop switch, by the gate signal input circuit with BNC connector on the front pannel. For Counter only and by a common line signal through the standard ORTEC printing loop IN/OUT connector on the rear pannel.

In T.C. mode the preset time function is enabled by setting the Preset M-thumb wheel at any digit between 1 and 9 and by selecting a decade multiplier 10 through 105 by setting the Preset N-thumb wheel at any digit between 0 and 5, the T.C. stops all other Counters that are included in the printing loop whenever its time level reaches the combination that is selected. The preset time can be disabled by setting both Preset M and N at digit 0, the unit then functions as a counter only. If the Counter is allowed to overflow, this overflow is shown by an LED on the front panel; the indicator remains lit from the first overflow until the unit is reset. At each overflow an output pulse is also furnished through a rear panel connector and may be used for connection to another Counter for an increased counting capacity.

When power is first applied to the unit, reset is generated automatically by a signal through a rear panel BNC connector or through a common line in the standard ORTEC printing loop through the In/Out connector on the rear panel.

The seven segments in each of the six characters of the

digital display can be tested at any time by pressing the Display Test switch on the front panel. When this switch is pressed, all seven segments in each digit should light to provide a reading of 888 888.

Master/Slave selects the function control of this module when it is connected in a standard ORTEC printing loop. The T.C. responds to a common preset signal or furnishes it for any switch position and also responds to local gate control and reset for any switch position. But with the switch set at Master, this module can also furnish gate control and reset to all slave modules in the system. When the switch is set at Slave, this module accepts gate control and reset from the system common lines.

#### 2.2 DATA TRANSFER SYSTEM [3]

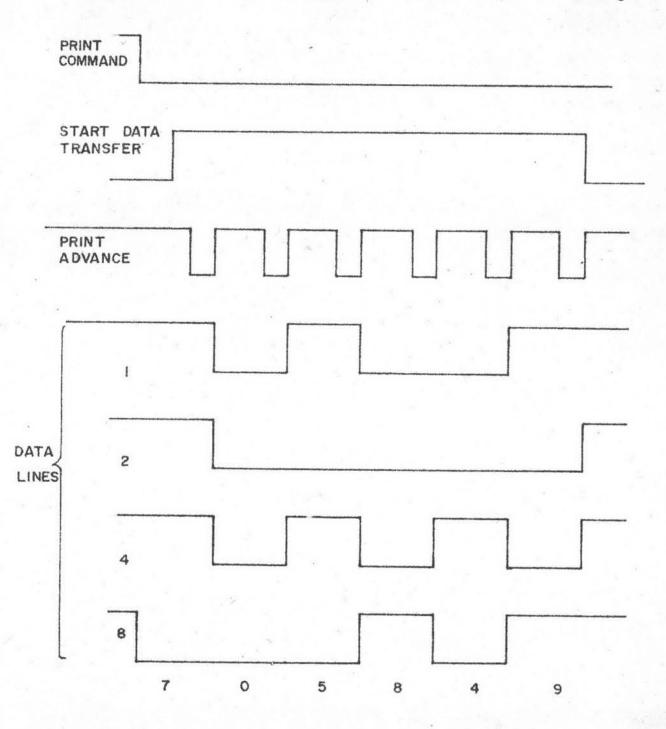

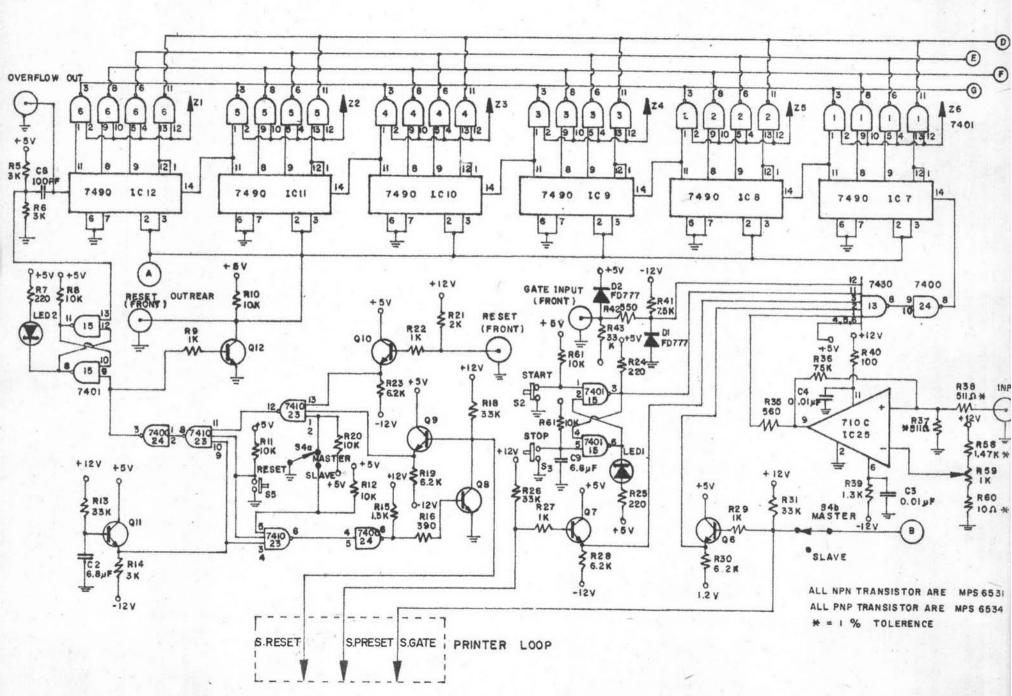

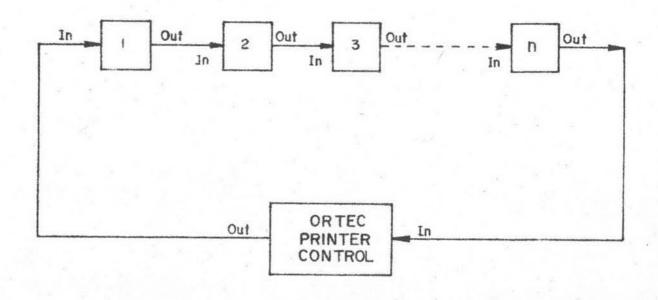

In normal operation all Counters and Timers in the system can count until a system set signal occurs; then all modules stop accumulating and the accumulated data are transferred out to a printer, one module at a time. The signal sequence for transferring Data for 705849 from a printing scaler is shown in Fig. 2.1. The Print Command signal ariginales in the printout Control Module such as the OFFEC 432 A or or OFFEC 777. It can be initiated manually, be triggered externally or be initiated automatically in the system reaching a preset time condition. The Start Data Transfer is supplied from The Printout Control to Counter 1, from Counter 1 to Counter 2 etc. In the system the Start Data Transfer

FIG.2.1 Signal Sequence for Transferring Data for 705849.

signal from the Printout Countrol is called Previous Module Finish (PMF) at the input of the Timer/Counter and is called "This Module Finish" (TMF) at the output of the T.C.

The following sequence of events illustrates how a multiple -counter printing system operates:

- A Print Command is generated manually, by a trigger or by a preset condition.

- 2. All modules in the system stop accumulating and remain static for 1 or 2 sec.

- 3. All displays are blank except the MSD in the display of Counter 1, this digit is lighted until the digit has been accepted by the output device.

- 4. Each of the remaining five digits in Counter 1 is printed in succession and as each digit is being printed, it is also illuminated in the display of the counter.

- 5. A space or a line feed is generated (depending upon the type of the Control unit under using) in the printed format after the six digits that represent the data in Counter 1.

- The six digits for Counter 2 are printed in succes-..

sion, a space or line feed is generated as in step 5.

- 7. This sequence repeats until the last counter has . . . finished printing.

- 8. After the last set of data has been printed the system will remain in a static or noncounting mode until a new cycle is initiated and the display will be turned on.

#### 2.3 CIRCUIT DESCRIPTION

#### 2.3.1 General

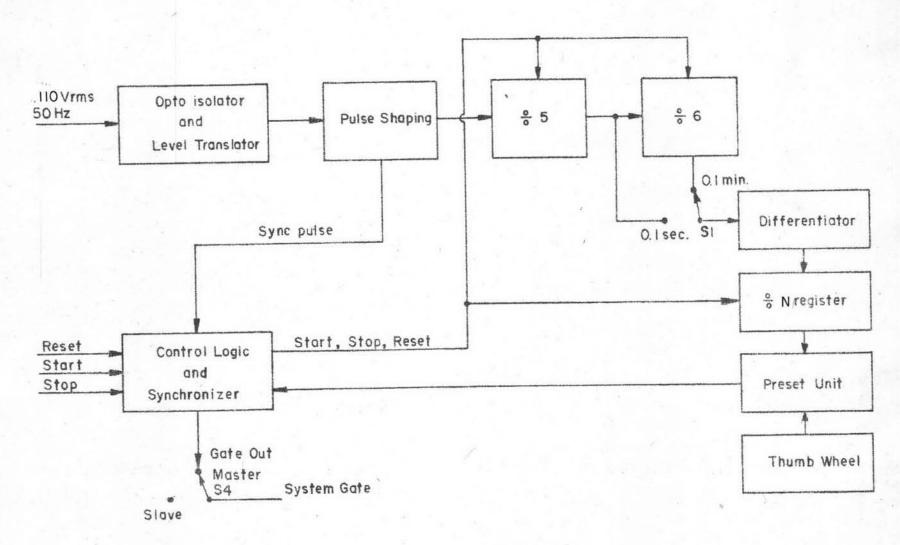

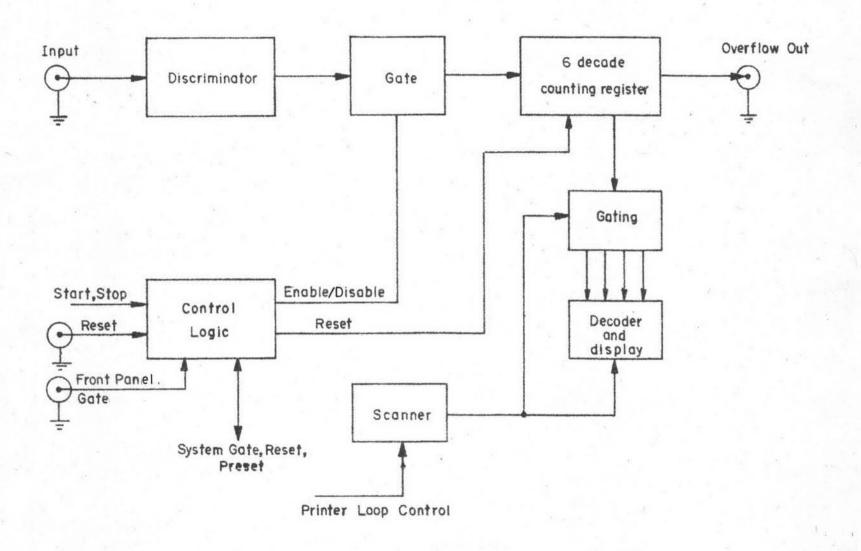

The T.C. is a precision timer with built in counter. The counter is a 6-decade ripple scaler preceded by a precise linear discriminator and includes logic for gating. The block diagram are shown in Fig. 2.2 and 2.3. For more details the complete schematic is shown in Fig. 2.4,2.5 and 2.6. As shown in Fig. 2.2 the timing pulses that are counted by the timer portion are dervied from the line frequency. These pulses are passed through a synchronizer before enabling the gate and through a count down circuit to provide on output at either 0.1 sec. or 0.1 min. intervals. The purpose for synchronization is to prevent ambiguity of pulse recognition at the start of the gate. The preset unit then counts down pulses from the divider (counting register) and after the preset is reached then inhibits the gate. The timer portion is reset to zero, together with the main counting register, by any reset that originates locally or from the system.

In the counter portion shown in Fig. 2.3 in-put pulses that pass through the discriminator and gate are sent to the counting register to be collected. The 24 data lines, for the six 4-bit word groups from the counting register, are gated one word at a time to the four common data lines. These data lines lead to a decode for the display and to the output for the printing loop.

An internal scanner gates the four bits for a digit onto the four

FIG.2.2 Block Diagram of The Timer Board.

FIG.2.3 Block Diagram of The Counter Board.

common lines and also selects the proper location in the display for that digit. During non printing intervals the scanner is driven by an internal oscillator that operates at about 1 KHz and continually recycles the scan through the six digits. During printing intervals the internal oscillator is turned off and the scan is advanced at the rate of the printing accessory.

The control logic block is the same for both unit.

It also includes routing to and from the system lines according to selection that is made with the Master/Slave switch.

#### 2.3.2 Timer

# 2.3.2.1 Optical Isolator and Level Translator

The optical isolator consists of diode P1, neon tube NE1, compound photo transistor Q1 and R1. Line voltage of 110V<sub>rms</sub> 50 Hz is rectified by D1, and NE1 is turned ON and OFF during each successive cycle. The photo transistor Q1 then translates the ON-OFF light into a train of pulses whose period corresponds to that of line frequency and the magnitude compatible to TTL level.

## 2.3.2.2 Pulse Shaping Circuit:

The circuit uses IC<sub>1</sub> a, an inverter, to speed up the rise and fall time of the pulses from the optoisolator circuit. To prevent an ambiguity that may arise due to some jitters that may impose on the signals during the switching of Q<sub>1</sub>, the falling edge of IC<sub>1</sub>a output then triggers IC<sub>2</sub>, a monostable multivibrator, giving a clear rectangular pulse the width of which

is about 10 m sec.

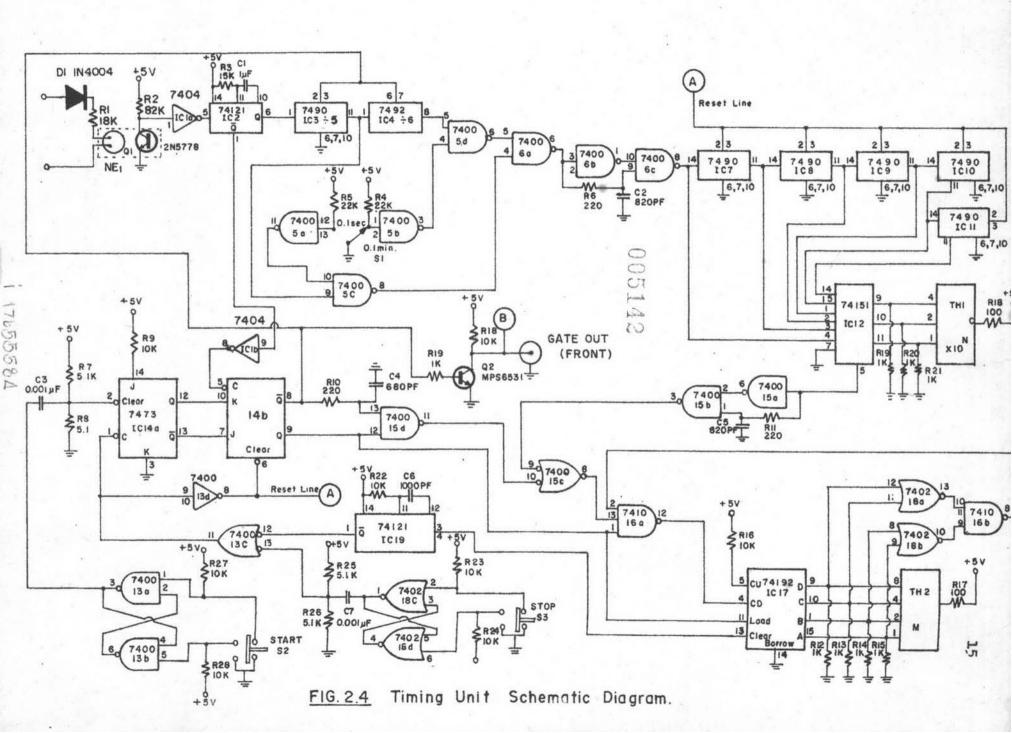

# 2.3.2.3 O.1 Sec., O.1 min. Selector, Differentiator and Divider Circuit (Fig. 2.4)

IC<sub>3</sub> and IC<sub>4</sub> scale down the input frequency by a factor of 5 and 6 corresponding to the setting of switch S<sub>1</sub> at 0.1 sec. and 0.1 min respectively. S<sub>1</sub> when in 0.1 sec.enables IC<sub>5</sub>c and disables IC<sub>5</sub>d, pulses whose period is 0.1 sec.are then passed to the differentiator circuit. For 0.1 min IC<sub>5</sub>c is disabled, thus pulses of 0.1 sec.period are further divided by 6 in IC<sub>6</sub> before entering the differentiator circuit. The differentiator composes IC<sub>6</sub> b,c,F<sub>6</sub> and C<sub>2</sub> and changes the pulse of long duration into a narrow clock pulse whose width is determined by R<sub>6</sub> and C<sub>2</sub>. The clock pulses are then applied to the divider circuit (IC<sub>7</sub> to 11) to be counted down in a multiple of ten from 10 to 10<sup>5</sup>.

## 2.3.2.4 Preset Circuit (Fig. 2.4)

Thumb wheel switches TH<sub>1</sub> and TH<sub>2</sub> preset the time in M x 10<sup>N</sup> style, where TH<sub>1</sub> selects the number of N and TH<sub>2</sub> the number of M. Data selector IC<sub>12</sub> selects pulse from the divider network whose location corresponds to the setting of N. For each pulse transmitted through IC<sub>12</sub>, a narrow negative pulse is obtained from IC<sub>15</sub> b output and being counted down by IC<sub>17</sub>, IC<sub>17</sub> then compares M with the number of pulses from IC<sub>12</sub>, and at the instant when M equal to the pulses counted a borrow signal is generated from IC<sub>17</sub>. The borrow signal then triggers the control circuit

to inhibit the gating circuit. TH<sub>2</sub> when in zero setting causes the outputs of IC<sub>18</sub> a and b to be High and IC<sub>16</sub>b to be Low thus preventing pulses from the selector IC<sub>12</sub> to be counted down in IC<sub>17</sub>, hence the timer portion has no influence upon the gating circuit and the module operates as a counter.

### 2.3.2.5 Control Logic (Fig.2.4)

To initiate the cycle S<sub>2</sub> is pressed, the latching action of IC<sub>13</sub>a and b causes a negative pulse at the clear input of IC<sub>14</sub>a. The Q output of IC<sub>14</sub>a then goes Low. IC<sub>14</sub>b forms a synchronizar to synchronize the initiating command and the edge of the first timing pulse. When synchronization begins Q output of IC<sub>14</sub>b is high. Also the output of the synchronizer is used to drive the gate buffer Q<sub>2</sub>.

The stop circuit. consists of IC18 c and d forming a switch debouncing circuit. When S3 is released negative edge is coupled through IC13 c and d to IC14, changes state of IC14 a and b thus closing the gate.

#### 2.3.3 Counter

## 2.3.3.1 Pulse input circuit (Fig. 2.5)

Positive input signals in the range of 0.1 through 10 V can be applied through the front panel BNC Input Connector. They are d-c coupled through divider network R37 and R38 to the positive input of the comparator IC25. The negative input to IC25 is the d-c level selected with Discriminator Control R59 on the front panel. Each input pulse whose amplitude exceeds the dis-

criminating level will generate a logic output from IC<sub>25</sub> pin 9 to drive IC<sub>13</sub>. If the counter is not being reset and is in the counting condition the input pulse becomes a clock pulse into the last significant decade IC<sub>7</sub> and is counted.

#### 2.3.3.2 Gating (Fig. 2.5)

With no Gate input signal and the unit operates in counter mode only ie,  $TH_2$  is set at 0 or  $S_4$  set at Slave and the starting circuit is initiated ( $S_2$  is pressed),  $IC_{15}$  pin 3 goes High enabling gate  $IC_{13}$  to pass the signals from the discriminator to be accumulated in the data register ( $IC_7$  to  $IC_{12}$ ). When  $S_3$  is pressed  $IC_{15}$  pin 3 goes Low thus inhibiting the accumulation. Likewise, if there is a Gate input connection and the signal is dropped to  $\leq 1.5 V$   $IC_{13}$  pin 12 is Low and the gate is inhibited. If switch  $S_4$  is set at Master, system gate is then applied to the timer gate output and the Stop depends on the time interval of the timer board.

#### 2.3.3.3 Counting Register (Fig. 2.5)

The counting register includes decade counter IC7 through IC12. They are connected to form a ripple counter for all six digits of the 999 9990 ount capacity. IC7 is the least significant digit and IC12 is the most significant digit. The BCD identification of each digit is carried through four lines to a set of gates that will pass the identity through the four common BCD lines when gated by the scanner. The overflow from IC12 pin 11 is coupled through C1 to the latching network IC15 c and d.

The first overflow after a reset will trigger the latch to drive LED2. The overflow output is obtained from the front panel BNC connector.

#### 2.3.3.4 Scanner (Fig. 2.6)

The scanner generates the Z1 through Z6 signals in sequence. It gates the most significant digit onto the common lines first with Z1, then it gates each less significant digit in order through Z6. When no print signal is furnished from the printer loop (nonprinting condition) an interval oscillator advances the scanner. When a print signal is present (printing interval), the scanner counts Print Advance input signals between the PMF and TMF signals, it scans through the available digits only one time during the printing cycle. The interval oscillator uses IC22 a and b to generate on output signal at about 1 KHz. The output feeds through IC21 pin 3 and 6 unless a print signal is present and to the clock input of IC19 pin 1. The binary output IC19 is fed to the 4 to 16 line decoders IC17 used as a 3 to 6 line decoders. When all the three bits at the input of IC17 are zero, it identifies zero at pin 1, this generates  $\mathbb{Z}_1$  at  $\mathrm{IC}_{17}$  pin 1 and  $\mathbb{Z}_1$  at  $\mathrm{IC}_{16}$  pin 8. The next oscillator pulse changes the count for a  $\bar{z}_2$  at  ${\rm IC}_{17}$  pin 2 and  $Z_2$  at  $IC_{16}$  pin 2. This sequence signal operation continues until each signal has been generated in turn and an oscillator pulse advances the counter out of its  $Z_6$  condition and back to  $Z_1$ and the scanning is recycled immediately.

# 2.3.3.5 Decode and Display (Fig. 2.6)

The four bits that are present on the common lines

FIG.26 Schematic Diagram for Strobing Display and Printout Control.

at any time represent one of the digits. This combination is decoded in ICA1 and furnishes the correct configuration of blanking and illumination to the seven LED segments at the anodes of all six digits in the display LEDA3 and LEDA4. The scanner signal will have selected which of the six digits in the counting register is gated onto the four common lines, and the same signal completes the cathode path of the proper digit in the display. For example when Z6 is present, the cathode of the least significant digit in the display is selected, and the digit is identified through IC14 the four common lines, and ICA1 to the segments of LEDA3 for that digit.

For reference, the seven segments are identified a through g. Viewed from the front of the display as shown in Fig.2.7 Any digit between 0 and 9 can be obtained by selective blanking of these segments. When switch S6 is pressed ICA1 provides no blanking for any segment and the display should illuminates all segments for a reading of 888 888 ICA3 pin 11 provides for automatic blanking of insignificant zeros in the display. At Z1 time, for the most significant digit, IC1, receives a signal from ICA3 pin 6 to blank all segments if all inputs to IC1 are low. Internal logic in ICA1 (RBO) resets the blanking control through ICA3 pin 8 when it identifies any digit other than zero from the four common lines. So until there is a digit that is non zero, nothing can be shown in the display. When the scan reaches Z6 the signal at ICA3 pin 11 will remove the automatic blanking leaving the least significant digit to be always displayed.

FIG. 2.8 Timer-Counter Interconnection for System Operation.

#### 2.3.3.5 Printing Circuit (Fig. 2.6)

A printing loop is formed by cabling the printing modules and either an ORTEC 777 Line Printer or 432A Printout Control in a circuit as shown in Fig. 2.8.

In the T.C. the system preset is accepted through Q7 of the counter board to turn off the input gate IC13 pin 8. This prevents any advance of the counting register. The print signal is accepted through pin 5 of the In (Out) connector and Q1 to inhibit oscillator gate IC21 pin 3 to reset the scanner to Z1 through IC20 pin 6, IC21 pin 8 and IC20 pin 8 and to clamp all four gates of IC14 to provide a "code 15" input to ICA1 that blanks the display. The module then waits until its turn to be printed out. A Previous Module Finish (PMF) input from the printer loop signals the printing cycle for the module. The PMF originates in the control module if the T.C. is Counter 1 and the system of Fig. 2.6 or is the TMF output from the previous Counter for any of the other positions in the loop. The PMF input releases the reset latch at IC21 pin 8, releases the blanking clamp to IC14 and enables gate ICA7 to transfer the data from the four commen lines in the T.C. to the system common lines. The most significant digit is gated from IC12 through IC6 by Z1 for transfer to the Printer and to the display. At print advance, when the digit has been accepted by the Printer, the signal through Q5 and IC21 pin 6 advances IC19 for the Z2 digit that is in IC11. Each subsequent print advance selects the next digit until Z6, after which IC18

generates a TMF output and restores the off-line condition of the T.C. When the last module in the loop furnishes TMF to the next control module, the control module determines the next sequence. It can remove preset, generate reset, or whatever is appropriate to the program that has been selected.

# 2.3.3.6 Master/Slave Circuits (Fig. 2.5)

Switch  $S_4$  selects the mode of operation for this function. When the switch is set at Master, internal reset and gate signals are furnished to the system reset and gate lines for control of any other modules that are for Slave.

With S<sub>4</sub> set at Master, IC<sub>23</sub> pin 12 is held High, thus prevents system reset to enter IC<sub>23</sub> pin 8. If Reset push button S<sub>5</sub> is pressed a reset signal is generated via IC<sub>23</sub> pin 8, IC<sub>24</sub> pin 3, Q<sub>12</sub> collector to reset the module and to drive the system reset line via IC<sub>23</sub> pin 6 IC<sub>24</sub> pin 6 and Q<sub>8</sub>.

If  $S_4$  is set at Slave, timer gate out is disconnected from the system gate by  $S_4$  and the module loses control upon other modules in the system. Since  $IC_{23}$  pin 6 is held High, module reset cannot pass through  $IC_{23}$  pin 6,  $IC_{24}$  pin 6 and  $Q_8$  to the system reset.

#### 2.3.3.7 Local Reset (Fig. 2.5)

Local reset is generated at IC<sub>23</sub> pin 8 if any of its inputs goes Low. The inputs originate with switch S<sub>4</sub>, from Reset BNC through Q<sub>10</sub>, IC<sub>23</sub> pin 12, from Q<sub>11</sub> at the time power is first applied to the unit, or from the system reset line through IC<sub>23</sub> pin 12.

## 2.3.3.8 Power Supply

The unit derives the power supply from the NIM Power Supply which provides a ±12 V DC at 2A, ± 24 V DC at 1A and 115 V AC. The + 5 V DC required by the digital IC's is obtained from the regulator circuit.