## รายการอ้างอิง

- Larmarsh, J.R. <u>Introduction to nuclear engineering</u>. 2nd ed. California: Addison-wesley publishing company, 1983.

- 2. Hussein, E.M.A. Scattering of alpha, beta, and gamma radiation for chemical analysis.

In Z.B. Alassi (ed.), Chemical Analysis by Nuclear Methods, pp. 417-430

- Robin, P.G. and Ralph L.F.Jr. Radiation Measurement Application in Engineering.

United State of America: Reinhold Publishing, 1967.

- 4. Reed, S.J.B. Electron microprobe analysis. London: Cambridge university press, 1975.

- 5. Gonzalez, R.G. and Woods, R.E. <u>Digital image processing</u>. Massachusetts: Addision-wesley, 1992.

- 6. Gayler, W.D. The apple2 circuit decription. Indianapolis: Howward W. Sams ,1983.

- 7. Microprocessor data book MCS-51 microcontrollers. ETT.Bangkok:

### บรรณานุกรม

- 1. Jacob Millman, Ph.D. and Chirstos C. Halkias, Ph.D. Intergrated electronics. Singapore:

Mcgraw-Hill Book, 1972.

- 2. Knoll ,G.F. Radiation detection and measurement. 2nd ed. New York: John Wiley & son, 1976.

- 3. Nicholson, J.W. Nuclear electronics. London: A wiley-interscience publishing, 1974.

- Tu, S. and Sato, O. locating the position of reinforcing bars in reinforced concrete

using backscattered gamma rays. Applied Radiation and Isotopes.

(September 1990): 1013-1018.

- 5. Stout, D.E. and Kaufman, M. Handbook of operational amplifier circuit design. New York: Mcgraw-Hill book.1976.

- 6. Linear circuit data book. USA: Texas instruments incorporated, 1992.

- 7. CMOS logic data. USA: Motolora incorporated, 1991.

- 8. Boylestad, R. and Nashelsky, L. <u>Electronic devices and circuit theory</u>. 4th ed. London: Prentice-Hall International, 1972.

- 9. Microprocessor data handbook. UAE: Micro-Tech, 1992.

### ภาคผนวก ก

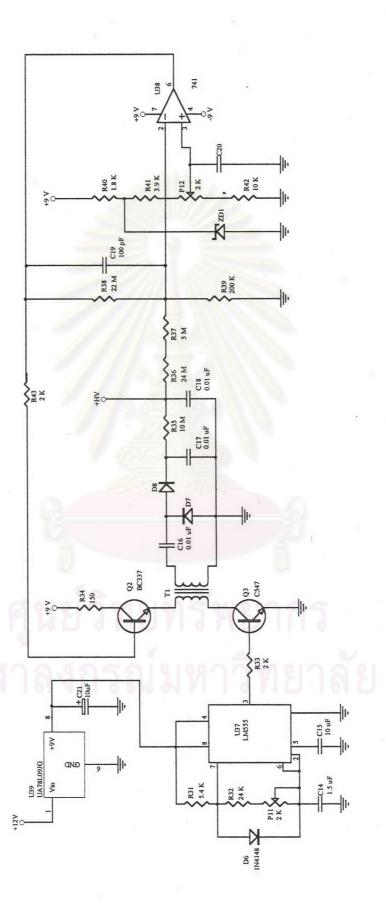

# การออกแบบและคำนวณหม้อแปลงไฟฟ้าศักคาสูง

แหล่งจ่ายไฟฟ้าศักคาสูงที่ใช้สำหรับหัววัครังสีไกเกอร์ ซึ่งใช้กระแส 10 ไมโคร แอมแปร์ งานวิจัยนี้จึงเลือกใช้หม้อแปลงแกนเฟอร์ไรต์แบบ EP ขนาด 13 ตารางมิลลิเมตร ,  $A_{\rm e}$  = 0.195 cm 2 , $\Delta B$  = 1500 และกำหนดการทำงานต่างๆ ดังนี้ คือ ศักคาไฟฟ้าทางค้านเข้า 9 โวลต์ ให้ศักคาไฟฟ้าค้านขาออก 100 โวลต์ ช่วงเวลา  $t_{\rm m}$  = 9 ไมโครวินาทีและประสิทธิภาพ ของหม้อแปลง 80 เปอร์เซ็นต์ ขั้นตอนการออกแบบมีคังนี้

$$T = \frac{1}{f}$$

$$= \frac{1}{16kHz}$$

$$= 62.5 \,\mu s$$

$$t_{on(max)} = \frac{(V_O + V_D)(N_P / N_S)(0.8T)}{(V_{in(max)} - V_{CE(sat)}) + (V_O + V_D)(N_P / N_S)}$$

$$31.25 \times 10^{-6} = \frac{(100 + 0.7)(N_P / N_S)(0.8 \times 62.5 \times 10^{-6})}{9 + (100 + 0.7)(N_P / N_S)}$$

$$\frac{N_P}{N_S} = 0.1489$$

$$\frac{N_S}{N_P} = 6.713$$

$$L_P = \frac{\eta \left[ (v_{in(max)} - V_{CE(sat)}) \times t_{on(max)} \right]^2}{2T \times PoUT}$$

$$= \frac{0.8 \left[ (9 - 0.7) \times 31.25 \times 10^{-6} \right]^2}{2 \times 62.5 \times 10^{-6} \times 100 \times 10 \times 10^{-6}}$$

$$= 430 \,\text{mH}$$

$$I_P = \frac{(9 - 0.7) \times 31.25 \times 10^{-6}}{L_P}$$

$$= \frac{(9 - 0.7) \times 31.25 \times 10^{-6}}{430 \times 10^{-3}}$$

$$= 603 \,\mu\text{A}$$

$$N_{P} = \frac{(V_{in(max)} - V_{CE(sat)} \times t_{on(max)} \times 10^{8}}{\Delta B A_{e}}$$

$$= \frac{(9 - 0.7) \times 31.25 \times 10^{-6} \times 10^{8}}{1500 \times 0.195}$$

$$= 88 501$$

$$N_{S} = 6.7 \times N_{P}$$

$$= 595 501$$

ศูนย์วิทยทรัพยากร จุฬาลงกรณ์มหาวิทยาลัย

### ภาคผนวก ข

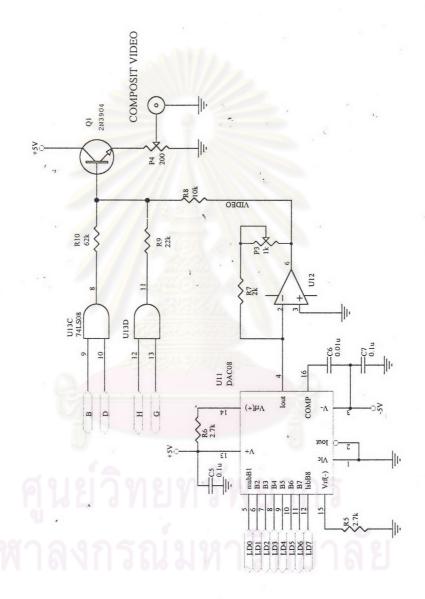

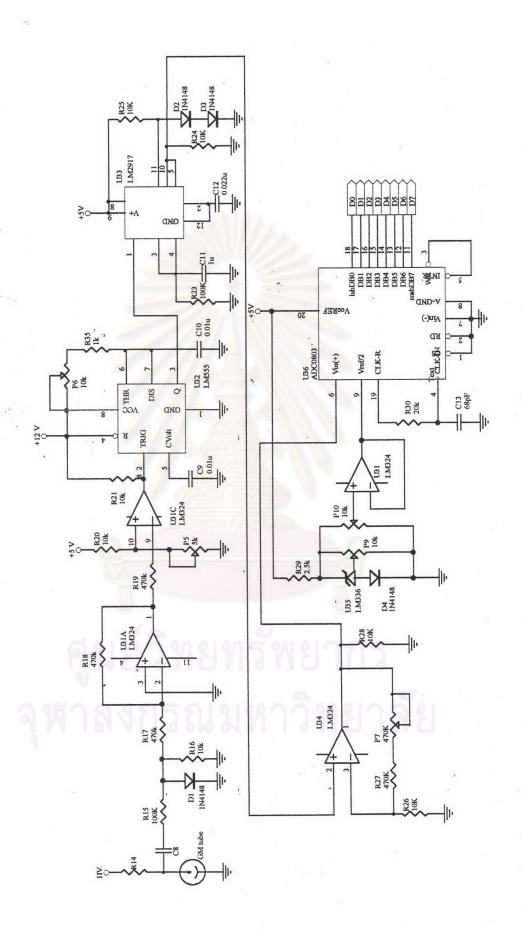

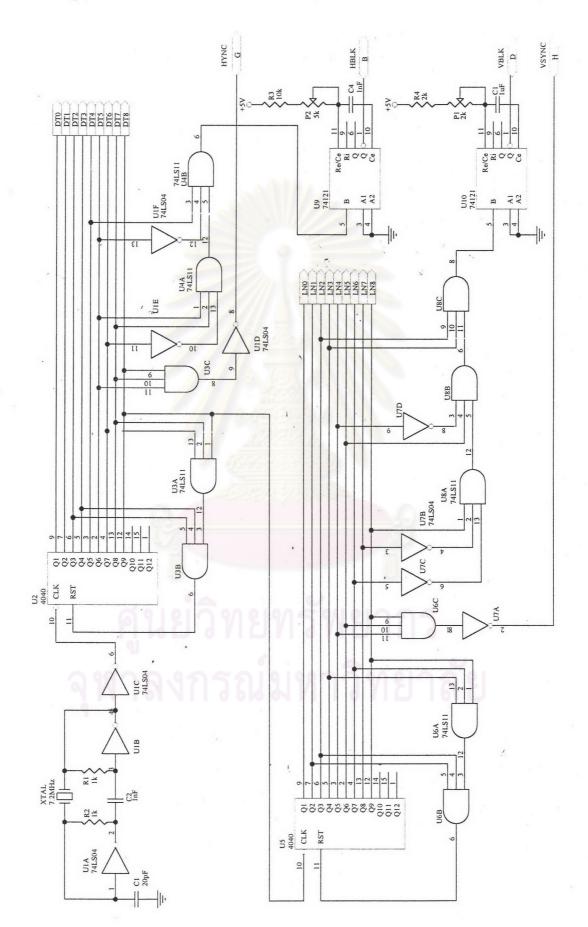

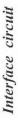

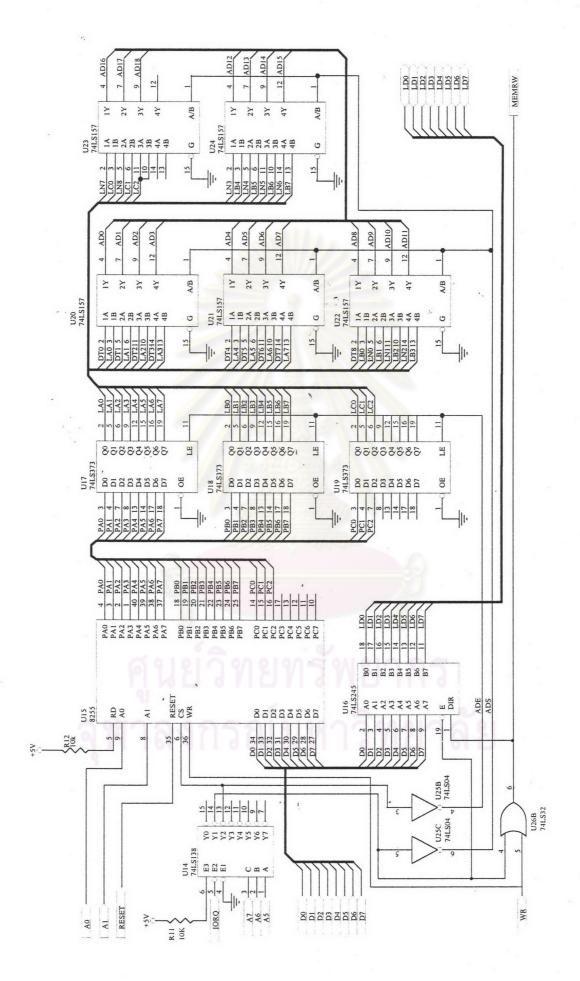

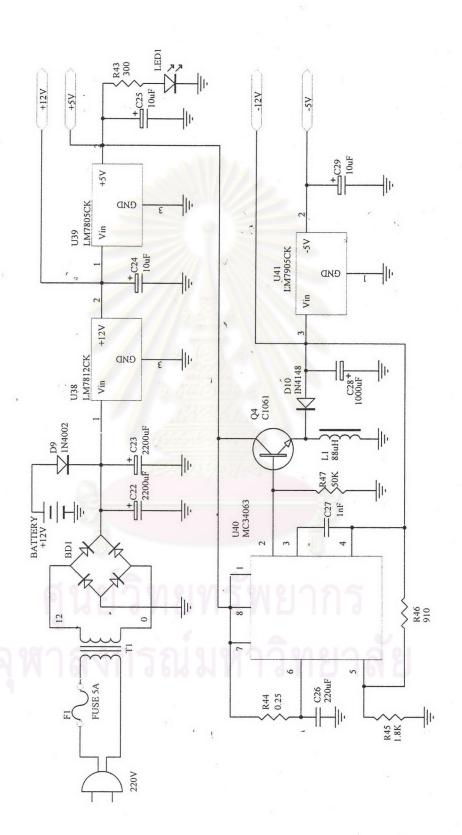

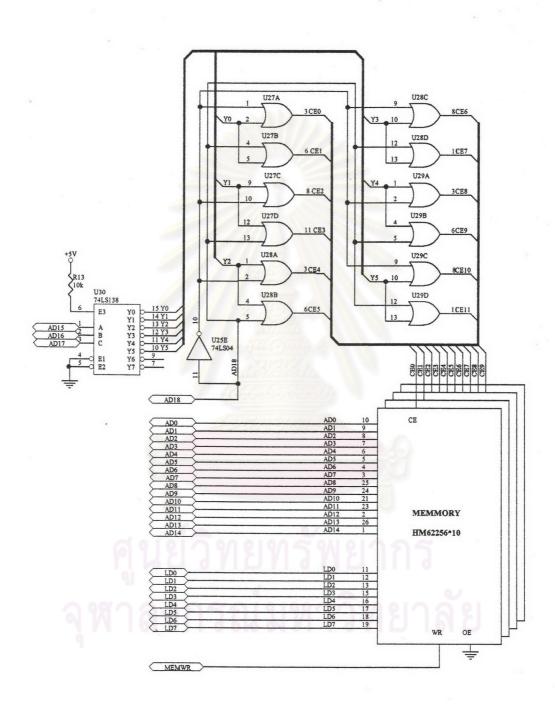

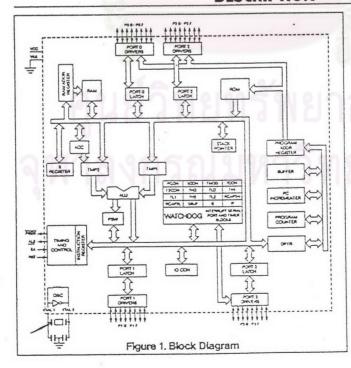

# วงจรอิเล็กทรอนิกส์ของระบบสแกนรังสึกระเจิงกลับเพื่อแสคงภาพสองมิติ

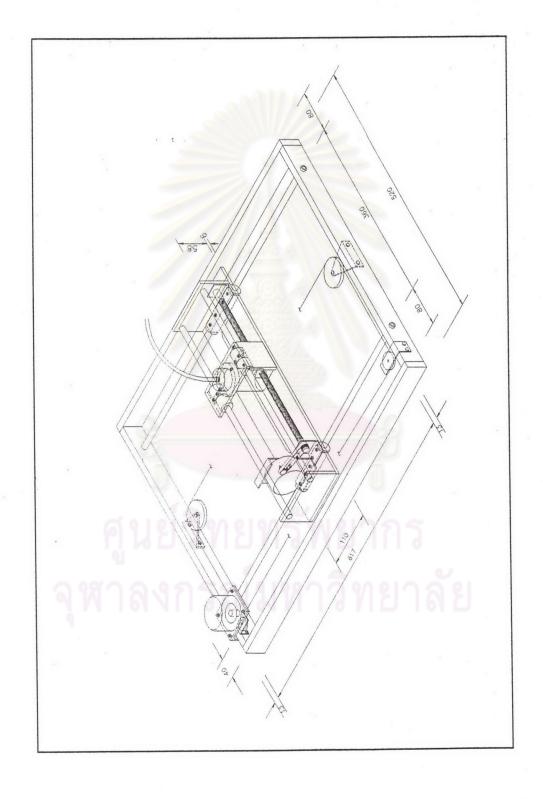

ภ**าคผนวก ค** แบบโครงสร<sup>้</sup>างอุปกรณ**์**ขับเคลื่อนทางกล

#### ภาคผนวก ง

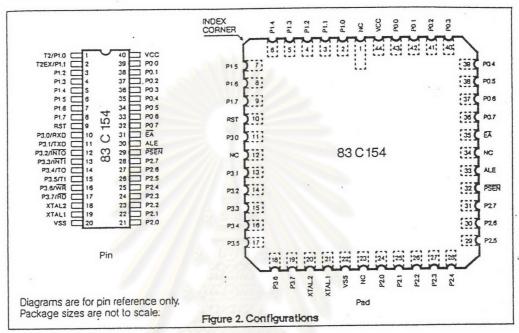

# ขอมูลทางเทคนิคของใมโครคอนโทรลเลอร์ 83C154

PRELIMINARY

AUGUST 1988

# DATA SHEET

83CT54

## CMOS SINGLE - CHIP 8 BIT MICROCONTROLLER

- 83C154 CMOS SINGLE-CHIP 8-BIT MICROCONTROLLER with factory mask-programmable ROM

- 83C154F-The internal ROM code cannot be read or dumped after activation of a special protection

- 80C154 ROMLESS version

- 83C154-1-16 MHz version

- 80C154-1-16 MHz ROMless version

#### **FEATURES**

- 16K x 8 BIT INTERNAL ROM

- 256 x BIT RAM

- 32 PROGRAMMABLE I/O LINES (PROGRAMMABLE IMPEDANCE)

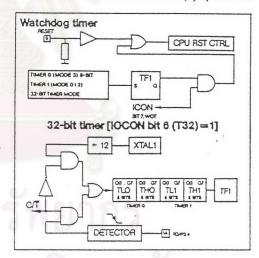

- THREE 16-BIT TIMER/COUNTERS (INCLUDING WATCH DOG AND 32 BIT TIMER)

- 64K PROGRAM MEMORY SPACE

- · FULLY STATIC DESIGN

- POWER CONTROL MODES

- INTERRUPT PRIORITY CONTROL

- 0 TO 16 MHz

- BOOLEAN PROCESSOR

- 6 INTERRUPT SOURCES

- PROGRAMMABLE SERIAL PORT

- . 64K DATA MEMORY SPACE

- . TEMPERATURE RANGE:

- COMMERCIAL

- INDUSTRIAL

#### DESCRIPTION

The 83C154 retains all the features of the MHS 80C52 with extended ROM capacity (16K bytes). 256 bytes of RAM, 32 I/O lines, a 6-source 2-level interrupts, a full duplex serial port, an on-chip oscillator and clock circuits, three 16 bit timers with extra features: 32 bit timer and watch dog functions. Timer 0 and 1 can be configured by program to implement a 32 bit timer. The watch dog function can be activated either with timer 0, or timer 1 or both together (32 bit timer).

In addition, the 83C154 has two software selectable modes of reduced activity for further reduction of power consumption. In the Idle Mode, the CPU is frozen while the RAM is saved, and the timers, the serial port, and the interrupt system continue to function. In the Power Down Mode, the RAM is saved and the timers, serial port and interrupts continue to function when driven by external clocks. In addition as for the MHS 80C51/C52, the stop clock

mode is also available.

WWS

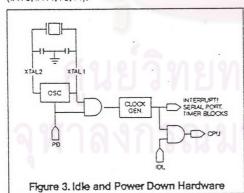

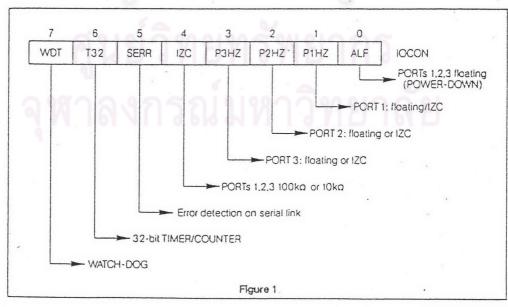

# IDLE AND POWER DOWN OPERATION

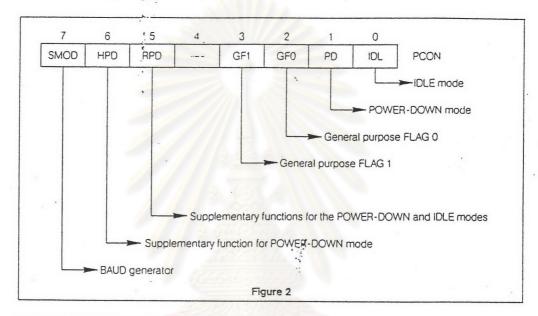

Figure 3 shows the internal Idle and Power Down clock configuration. As illustrated, Power Down operation stops the oscillator. The interrupt, serial port, and timer blocks continue to function only with external clock (INTO, INT1, TO, T1).

Idle Mode operation allows the interrupt, serial port, and timer blocks to continue to function with internal or external clocks, while the clock to CPU is gated off. The special modes are activated by software via the Special Function Register, PCON. Its hardware address is 87H. PCON is not bit addressable.

| (MSB) |     |     |   |     |     |    | (LSB) |

|-------|-----|-----|---|-----|-----|----|-------|

| SMOD  | HPD | RPD | - | GF1 | GF0 | PD | IDL   |

| Symbol | Position | Name and Function                                                                                                                                                                                                                                                                                        |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMOD   | PCON.7   | Double Baud rate bit. When set to a 1, the baud rate is doubled when the serial port is being used in either modes 1, 2 or 3.                                                                                                                                                                            |

| HPD    | PCON.6   | Hard Power Down bit. Setting this bit allows CPU to enter in Power Down state on an external event (1 to 0 transition) on bit T1 (p. 3-5) the CPU quit the Hard Power Down mode when bit T1 (p. 3-5) go high or when reset is activated.                                                                 |

| RPD    | ·PCON.5  | Recover from Idle or Power Down bit. When 0 RPD has no effect. When 1, RPD permits to exit from idle or Power Down with any non enabled interrupt source (except timex 2). In this case the program start at the next address. When interrupt is enabled, the appropriate interrupt routine is serviced. |

| -      | PCON.4   | (Reserved)                                                                                                                                                                                                                                                                                               |

| GF1    | PCON.3   | General-purpose flag bit.                                                                                                                                                                                                                                                                                |

| GF0    | PCON.2   | General-purpose flag bit.                                                                                                                                                                                                                                                                                |

| PD     | PCON.1   | Power Down bit. Setting this bit activates power down opera-                                                                                                                                                                                                                                             |

tion.

. PCON.O Ide mode bit. Setting this bit

activates idle mode operation.

If 1's are written to PD and IDL at the same time. PD takes, precedence. The reset value of PCON is (000X0000).

#### IDLE MODE

The instruction that sets PCON.0 is the last instruction executed before the Idle mode is activated. Once in the Idle mode the CPU status is preserved in its entirety: the Stack Pointer, Program Counter, Program Status Word, Accumulator, RAM, and all other registers maintain their data during Idle. In the Idle mode, the internal clock signal is gated off to the CPU, but interrupt, timer and serial port functions are maintained. Table 1 describes the status of the external pins during Idle mode.

There are three ways to terminate the Idle mode. Activation of any enabled interrupt will cause PCON.0 to be cleared by hardware, terminating Idle mode. The interrupt is serviced, and following RETI, the next instruction to be executed will be the one following the instruction that wrote 1 to PCON.0.

The flag bits GFO and GFI may be used to determine whether the interrupt was received during normal execution or during the kile mode. For example, the instruction that writes to PCON.0 can also set or clear one or both flag bits. When kile mode is terminated by an enabled interrupt, the service routine can examine the status of the flag bits.

The second way of terminating the Idle mode is with a hardware reset. Since the oscillator is still running, the hardware reset needs to be active for only 2 machine cycles (24 oscillator periods) to complete the reset operation.

The third way to terminate the Idle mode is the activation of any disabled interrupt when recover is programmed (RPD=1). This will cause PCON.0 to be cleared. No interrupt is serviced. The next instruction is executed. If interrupt are disabled and RPD=0, only a reset can cancel the Idle mode.

#### POWER DOWN MODE

The instruction that sets PCON.1 is the last executed prior to entering power down. Once in power down, the oscillator is stopped. The contents of the onchip RAM and the Special Function Register is saved during power down mode. The three ways to terminate the Power Down mode are the same than the Idle mode. But since the onchip oscillator is stopped, the external interrupts, timers and serial port must be sourced by external docks only, via INTO, INT1, TO, T1.

In the Power Down mode, VCC may be lowered to

minimize circuit power consumption. Care must be taken to ensure the voltage is not reduced until the power down mode is entered, and that the voltage is restored before the hardware reset is applied which frees the oscillator. Reset should not be released until the oscillator has restarted and stabilized.

When using voltage reduction: interrupt, timers and serial port functions are guaranteed in the VCC specification limits.

Table 1 describes the status of the external pins while in the power down mode. It should be noted that if the power down mode is activated while in external program memory, the port data that is held in the Special Function Register P2 is restored to Port 2. If the port switches from 0 to 1, the port pin is held high during the power down mode by the strong pullup, T1, shown in Figure 4.

#### STOP CLOCK MODE

Due to static design, the MHS 83C154 clock speed can be reduced until 0 MHz without any data loss in memory or registers. This mode allows step by step utilization, and permits to reduce system power consumption by bringing the clock frequency down to any value. At 0 MHz, the power consumption is the same as in the Power Down Mode.

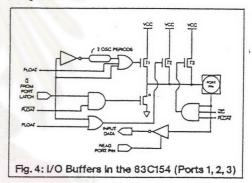

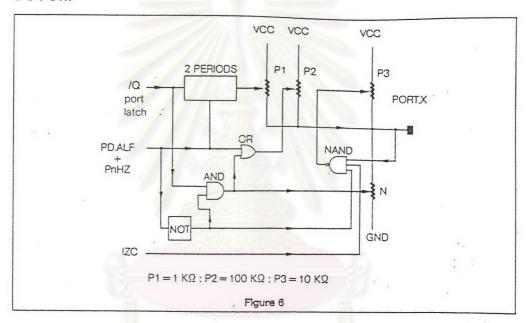

#### 83C154 I/O PORTS

The I/O drives for P1, P2, P3 of the 83C154 are impedance programmable. The I/O buffers for Ports 1.2 and 3 are implemented as shown in figure 4. When the port latch contains 0, all pFETS in figure 4 are off while the nFET is turned on. When the port latch makes a 0-to-1 transition, the nFET turns off The strong pullup pFET, T1, turns on for two oscillator periods, pulling the output high very rapidly. As the output line is

Table 1. Status of the external pins during Idle and Power Down modes

| Mode          | Program Memory | ALE | PSEN | PORTO     | PORTY     | PORT2     | PORT3     |

|---------------|----------------|-----|------|-----------|-----------|-----------|-----------|

| Idle          | Internal       | 1   | 1    | Port Data | Port Data | Port Data | Port Data |

| ldle          | External       | 1   | - 1  | Floating  | Port Data | Address · | Port Data |

| Power<br>Down | Internal       | 0   | 0    | Port Data | Port Data | Port Data | Port Data |

| Power<br>Down | External       | 0   | 0    | Floating  | Port Data | Port Data | Port Data |

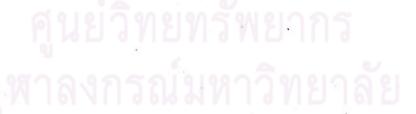

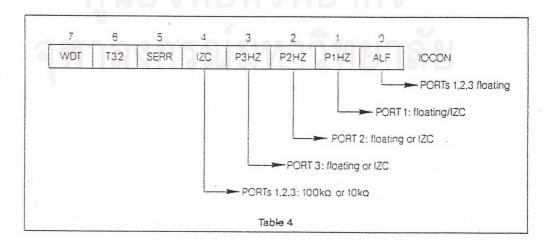

drawn high, pFET T3 turns on through the inverter to supply the IOH source current. This inverter and T3 form a latch which holds the 1 and is supported by T2. When Port 2 is used as an address port, for access to external program of data memory, any address bit that contains a 1 will have his strong pullup turned on for the entire duration of the external memory access. When an I/O pin on Ports 1, 2 or 3 is used as an input. the user should be aware that the external circuit must sink current during the logical 1-to-0 transition. The maximum sink current is specified as ITL under the D.C. Specifications. When the input goes below approximately 2V,T3 turns off to save ICC current. Note. when returning to a logical 1, T2 is the only internal pullup that is on. This will result in a slow rise time if the user's circuit does not force the input line high. The input impedance of Port 1, 2, 3 are programmable through the register IOCON. The ALF bit (IOCON0) set all of the Port 1,2,3 floating when a Power Down mode occurs. The P1HZ, P2HZ, P3HZ bits (IOCON1, IOCON2, IOCON3) set respectively the Ports P1, P2, P3 in floating state. The IZC (IOCON4) allows to choose input impedance of all ports (P1, P2, P3). When IZC = 0, T2 and T3 pullup of I/O ports are active; the internal input impedance is approximately 10K. When IZC=1 only T2 pull-up is active. The T3 pull-up is turned off by IZC. The

#### PIN DESCRIPTIONS

#### VSS

Circuit ground potential.

Supply voltage during normal, Idle, and Power Down operation.

internal impedance is approximately 100K.

#### PORT 0

Port 0 is an 8-bit open drain bi-directional I/O port. Port 0 pins that have 1's written to them float, and in that state can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external Program and

Data Memory. In this application it uses strong internal pullups when emitting 1's. Port 0 also outputs the code bytes during program verification in the 83C154 External pullups are required during program verification. Port 0 can sink eight LSTTL inputs.

Port 1 is an 8-bit bi-directional I/O port with internal pullups. Port 1 pins that have 1's written to them are pulled high by the internal pullups, an in that state can be used as inputs. As inputs, Port 1 pins that are externally being pulled low will source current (IIL, on the data sheet) because of the internal pullups. Port 1 also receives the low-order address byte during program verification. In the 83C154, Port 1 can sink/ source three LS TTL inputs. It can drive CMOS inputs without external pullups.

Port 2 is an 8-bit bi-directional I/O port with internal pullups. Port 2 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 2 pins that are externally being pulled low will source current (ILL, on

the data sheet) because of the internal pullups. Port 2 emits the high-order address byte during fetches from external Program Memory and during accesses to external Data Memory that use 16-bit addresses (MOVX @ DPTR). In this application, it uses strong internal pullups when emitting 1's. During accesses to external Data Memory that use 8-bit addresses (MOVX @Ri), Port 2 emits the contents of the P2 Special Function Register.

It also receives the high-order address bits and control signals during program verification in the 83C154. Port 2 can sink/source three LS TTL inputs. It can drive

CMOS inputs without external pullups.

Port 3 is an 8-bit bi-directional I/O port with internal pullups. Port 3 pins that have 1's written to them are pulled high by the internal pullups, and in that state can be used as inputs. As inputs, Port 3 pins that are externally being pulled low will source current (ILL, on the data sheet) because of the pullups. It also serves the functions of various special features of the MCS-51 Family, as listed below.

| Port Pin | Alternate Function |

|----------|--------------------|

|          |                    |

P3.0 RXD (serial input port) P3.1 TXD (serial output port)

P3.2 INTO (external interrupt 0) INT1 (external interrupt 1)

P3.3 P3.4 TO (Timer 0 external input)

T1 (Timer 1 external input)

P3.5 P3.6 WR (external Data Memory write strobe) P3.7 RD (external Data Memory read strobe)

Port 3 can sink/source three LSTTL inputs. It can drive CMOS inputs without external pullups.

A high level on this for two machine cycles while the oscillator is running resets the device. An internal pull-down resistor permits Power-On reset using only a capacitor connected to VCC.

Address Latch Enable output for latching the low byte of the address during accesses to external memory. ALE is activated as though for this purpose at a constant rate of 1/6 the oscillator frequency except during an external data memory access at which time one ALE pulse is skipped. ALE can sink/source 8 LS TTL inputs. It can drive CMOS inputs without an external pullup.

#### PSEN

Program Store Enable output is the read strobe to external Program Memory. PSEN is activated twice each machine cycle during fetches from external Program Memory. (However, when executing out of external Program Memory, two activations of PSEN are skipped during each access to external Data Memory). PSEN is not activated during fetches from internal Program Memory. PSEN can sink/source 8 LS-TTL inputs. It can drive CMOS inputs without an external pullup.

When EA is held high, the CPU executes out of internal Program Memory (unless the Program Counter

exceeds 3FFFH). When EA is held low, the CPU executes only out of external Program Memory. EA must not be floated.

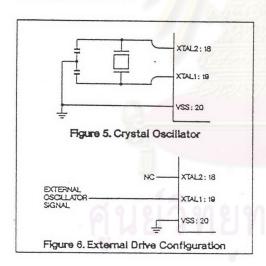

#### XTAL1

Input to the inverting amplifier that forms the oscillator. Receives the external oscillator signal when an external oscillator is used.

#### XTAL2

Output of the inverting amplifier that forms the oscillator. This pin should be floated when an external oscillator is used.

#### OSCILLATOR CHARACTERISTICS

Sheet must be observed.

XTAL 1 and XTAL 2 are the input and output respectively, of an inverting amplifier which is configured for use as an on-chip oscillator, as shown in figure 5. Either a quartz crystal or ceramic resonator may be used. To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected as shown in figure 6. There are no requirements on the duty cycle of the external clock signal, since the input to the internal clocking circuitry is through a divide-by-two flip-flop, but minimum and maximum high and low times specified on the Data

#### PORT 1 SECONDARY FUNCTIONS

This is a quasi-bidirectional I/O port, internally pulled up when used as input ports. Two of the ports have been allocated a second function which are:

P1.0 [T2]: External clock input for timer/counter 2. P1.1 [T2EX]: A trigger input for timer/counter 2, to be reloaded or captured causing the timer/counter 2 interrupt.

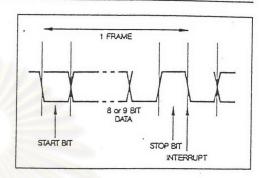

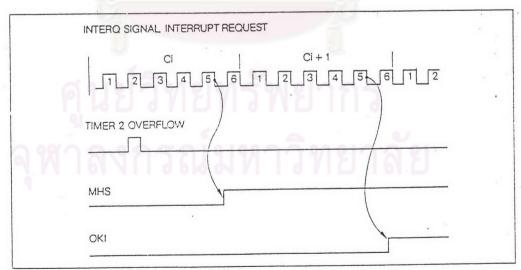

#### INTERRUPT MODES

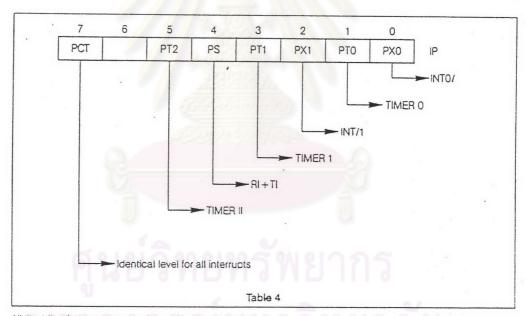

The MHS 80C154/83C154 is capable of handling two external interrupts, three interrupts from the timers, and, one interrupt from the serial port, through its incorporated six source, two-level interrupt structure.

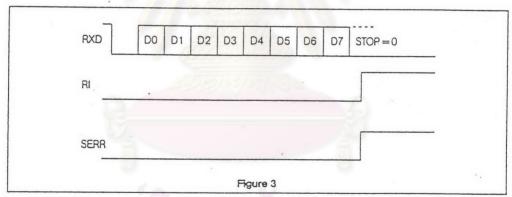

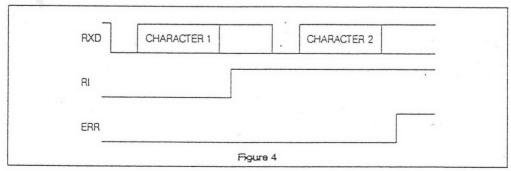

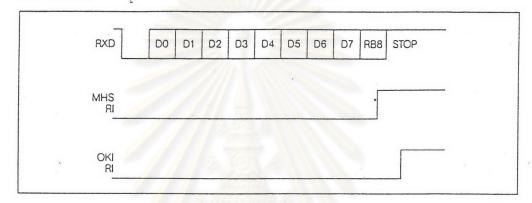

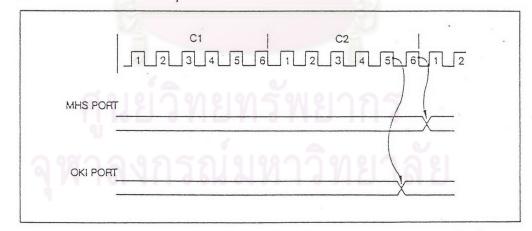

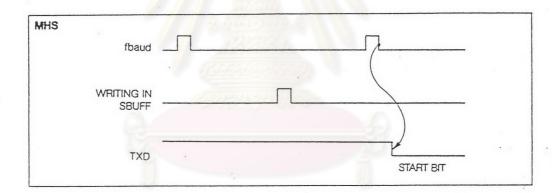

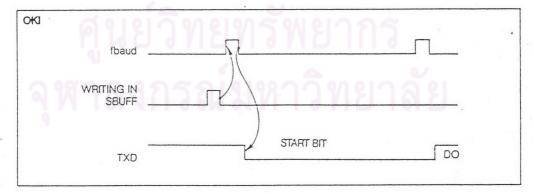

SERIAL PORTTIMING

The interrupt is executed after the Stop Bit.

#### TIMER FUNCTIONS

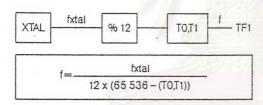

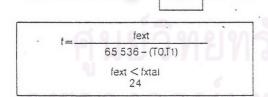

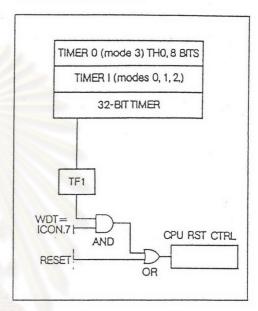

In fact, timer 0 & 1 can be connected by a software instruction to implement a 32-bit timer function. Timer 0 (mode 3) or timer 1 (mode 0, 1, 2) or a 32-bit timer consisting of timer 0 + timer 1 can be employed in the watchdog mode, in which case a CPU reset is generated upon a TF1 flag.

generated upon a TF1 flag.

The internal pull-up resistances at ports 1 ~ 3 can be set to a ten times increased value simply by software.

#### TIMER/EVENT COUNTER 2

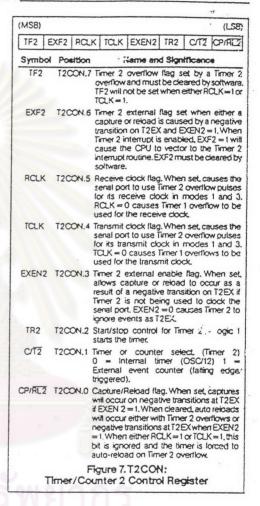

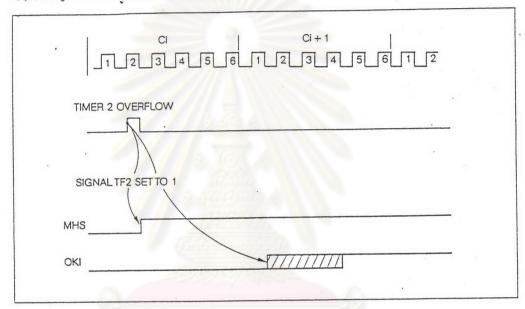

Timer 2 is a 16-bit timer/counter like Timers 0 and 1, it can operate either as a timer or as an event counter. This is selected by bit C/T2 in the Special Function Register T2CON (Fgure 7). It has three operating modes: "capture", "autoload" and "baud rate generator", which are selected by bits in T2CON as shown in Table 2.

Table 2. Timer 2 Operating Modes

| RCLK+ | TCLK | CP/RL2 | TR2 | MODE                |

|-------|------|--------|-----|---------------------|

| 0     |      | . 0    | 1   | 16 bit auto-reload  |

| 0     |      | 1      | 1   | 16-bit capture      |

| 1     |      | X      | 1   | baud rate generator |

| X     |      | X      | 0   | (off)               |

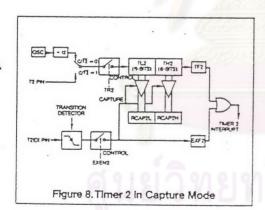

In the capture mode there are two options which are selected by bit EXEN2 in T2CON. If EXEN2 = 0, then Timer 2 is a 16-bit timer or counter which upon overflowing sets bit TF2, the Timer 2 overflow bit, which can be used to generate an interrupt. If EXEN2 = 1, then Timer 2 still does the above, but with the added feature that a 1-to-0 transition at external input T2EX causes the current value in the Timer 2 registers, TL2 ans TH2, to be captured into registers RCAP2L and RCAP2H, respectively. (RCAP2L and RCAP2H are new Special Function Registers in the 80C52). In addition, the transition at T2EX causes bit EXF2 in T2CON to be set, and EXF2, like TF2, can generate an interrupt. The capture mode is illustrated in Figure 8.

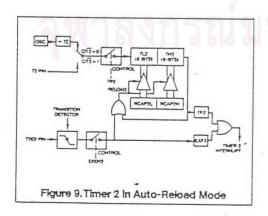

In the auto-reload mode there are again two options, which are selected by bit EXEN2 in T2CON.If EXEN2 = 0, then when Timer 2 rolls over it not only sets TF2 but also causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2L and RCAP2H, which are preset by software. If EXEN2=1, then Timer 2 still does the above; but with the added feature that a 1-to-0 transition at external input T2EX will also trigger the 16-bit reload and set EXF2.

The auto-reload mode is illustrated in Figure 9. The baud rate generator mode is selected by: RCLK=1 and/or TCLK=1.

83C154

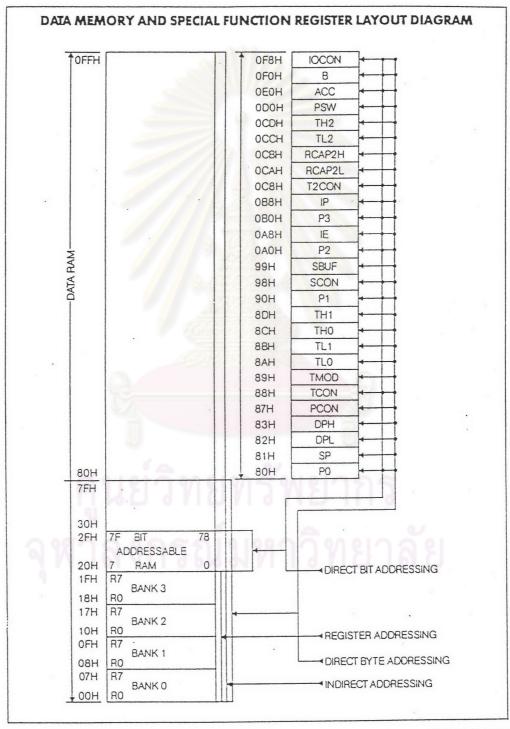

#### DETAILED DIAGRAM OF DATA MEMORY (RAM) OFFH 7FH 2FH 7F 7E 7C **7B 7A** 2EH 2DH 6F 6C 6A 6E 2CH 28H 5F 5B 5E 5D 5C 5A DIRECT BYTE ADDRESSING DIRECT BIT ADDRESSING 2AH INDIRECT ADDRESSING 29H 4F 4E 4C 4B 4A 28H 27H 3F 3E 3C 3A 26H 25H 2F 2E 2C 2A 24H 23H 1F 1E 1C 1A 22H 21H OF 0E OD OC OA 20H .06 1FH Bank 3 REGISTER ADDRESSING 18H 17H Bank 2 10H OFH Bank 1 08H 07H Bank 0 00H

| 0 | 2 | ~ | 5 | , |

|---|---|---|---|---|

| · By | rect<br>rte<br>ddress |       |                        |      | Dit A    | ddress   |      |      |        | Special<br>Function<br>Register |

|------|-----------------------|-------|------------------------|------|----------|----------|------|------|--------|---------------------------------|

| ^(   |                       | (MSB) |                        |      | DIL AL   | Juless   |      |      | (LSB)  | Symbol                          |

|      |                       | WDT   | T32                    | SERR | IZC      | P3HZ     | P2HZ | P1HZ | ALF    |                                 |

| OF   | F8H                   | FF    | FE                     | FD   | FC       | FB       | FA   | F9   | F8     | IOCON                           |

| OF   | -он                   | F7    | F6                     | F5   | F4       | F3       | F2   | F1   | FO     | В                               |

| 08   | ЕОН                   | E7    | E6                     | E5   | E4       | E3       | E2   | E1   | EO     | ACC                             |

|      |                       | CY    | AC                     | FO   | RS1      | RSO      | OV   | F1   | Р      |                                 |

| 00   | ЮН                    | D7    | D6                     | D5   | D4       | D3       | D2   | D1   | DO     | PSW                             |

| 00   | . HOX                 |       |                        | No   | t Bit Ac | dressat  | nle  |      |        | TH2                             |

|      | CH                    |       |                        |      |          | Idressal |      |      |        | TL2                             |

| 00   | XBH                   |       |                        |      |          | dressat  |      |      |        | RCAP2H                          |

| 00   | AH                    |       |                        | No   | t Bit Ac | dressat  | ole  |      |        | RCAP2L                          |

|      |                       | TF2   | EXF2                   | RCLK | TCLK     | EXEN2    | TR2  | C/T2 | CP/RL2 |                                 |

| 00   | BH [                  | CF    | Œ                      | CD   | CC       | CB       | CA   | C9   | C8     | T2CON                           |

|      |                       | PCT   |                        | PT2  | PS       | PT1      | PX1  | PTO  | PXO    |                                 |

| 08   | 8H [                  | BF    | -                      | BO   | 8C       | 88       | BA   | 89   | 88     | IP                              |

| 08   | он [                  | 87    | B6                     | 85   | 84       | 83       | 82   | B1   | 80     | P3                              |

|      | 0                     | EA    |                        | ET2  | ES       | ET1      | EX1  | ETO  | EXO    |                                 |

| 0A   | 8H [                  | AF    | -                      | AD   | AC       | AB       | AA   | A9   | A8     | IE                              |

| 0A   | он [                  | A7    | A6                     | A5   | A4       | A3       | A2   | A1   | AO     | P2                              |

| 99   | н Г                   |       |                        | No   | t Bit Ad | dressab  | ile  |      |        | SEUF                            |

|      | L                     | SMO   | SM1                    | SM2  | REN      | TB8      | R88  | TI   | RI     |                                 |

| 98   | н Г                   | 9F    | 9E                     | 9D   | 9C       | 98       | 9A   | 99   | 98     | SCON .                          |

| 90   | н [                   | 97    | 96                     | 95   | 94       | 93       | 92   | 91   | 90     | P1                              |

|      | [                     |       |                        | 33   | J 7      | 30       | 32   | 01   | 50     |                                 |

| 80   | н Г                   |       | TWY STORY OF THE STORY | No   | t Bit Ad | dressat  | ile  |      |        | TH1                             |

| 80   | H                     |       |                        |      |          | dressab  |      |      |        | THO                             |

| 88   | Н                     |       | 0.10                   | No   | t Bit Ad | dressab  | le   |      |        | TL1                             |

| 8A   | н [                   |       |                        | No   | t Bit Ad | dressab  | le   | 2    |        | TLO                             |

| 89   | н [                   |       |                        | No   | t Bit Ad | dressab  | le   |      |        | TMOD                            |

|      |                       | TF1   | TR1                    | TFO  | TRO      | IE1      | IT1  | IEO  | ПО     |                                 |

| 88   | H [                   | 8F    | 8E                     | 8D   | 8C       | 88       | 8A   | 89   | 88     | TCON                            |

| 871  | 4                     |       |                        | No   | t Bit Ad | dressab  | le   |      |        | PCON                            |

| 83   | ц г                   |       |                        | No   | Rit Ad   | dressab  | Ja   |      |        | DPH                             |

| 82   | -                     |       |                        |      |          | dressat  |      |      |        | OPL                             |

| 81   | -                     |       |                        |      |          | dressab  |      |      |        | SP                              |

| 80   |                       | 87    | 86                     | 85   | 84       | 83       | 82   | 81   | 80     | P0                              |

|  | C |  |

|--|---|--|

|  |   |  |

|  |   |  |

# SPECIAL FUNCTION REGISTERS TIME MODE REGISTER (TMOD)

| NAME         | ADDRESS | TMSB                                                                                                                                                                                                                                                                                                          | 6              | 1 5                    | 1 4                         | 3            |                       |             | LSE    |  |

|--------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------------|-----------------------------|--------------|-----------------------|-------------|--------|--|

| TMOD         | 89H     | GATE                                                                                                                                                                                                                                                                                                          | C/T            | M1                     | MO                          | GATE         | C/T                   | 1<br>M1     | MO     |  |

| BIT LOCATION | FLAG    |                                                                                                                                                                                                                                                                                                               |                |                        |                             | CTION        | 1 01                  | 1 1111      | 1 1410 |  |

| TMOD.0       | МО      | M1                                                                                                                                                                                                                                                                                                            | МО             | Timer/co               | unter 0 mc                  |              |                       |             |        |  |

|              |         | 0                                                                                                                                                                                                                                                                                                             |                | +                      | er/counter                  |              |                       |             |        |  |

|              |         | 0 1 1 116-bit timer/counter.                                                                                                                                                                                                                                                                                  |                |                        |                             |              |                       |             |        |  |

|              |         | 1                                                                                                                                                                                                                                                                                                             | - 0 -          | 8-bit time             | auto reloa                  | ading.       |                       |             |        |  |

| TMOD.1       | M1      | 1                                                                                                                                                                                                                                                                                                             | 1              | Timer/cooland THO      | unter 0 sep<br>(8-bit) time | parated in   | to TLO (8-            | bit) timer/ | counte |  |

| TMOD.2       | Сл̄     | Timer/co<br>XTAL1 · 2<br>C/T=*0*                                                                                                                                                                                                                                                                              | divided        | count cloc             | k designat                  | ion contro   | ol bit.<br>ed to time | r/counter   | 0 wher |  |

|              |         | The exte                                                                                                                                                                                                                                                                                                      | rnal clos      | ck applied to C/T="1". | o the TO p                  | in is the in | nput applie           | ed to time  | r/     |  |

| TMOD.3       | GATE    | When this bit is "0", the TR0 bit of TCON (timer control register) is used to control the start and stop of timer/counter 0 counting.  If this bit is "1", timer/counter 0 starts counting when both the TR0 bit of TCON and INTO pin input signal are "1", and stops counting when either is changed to "0". |                |                        |                             |              |                       |             |        |  |

| TMOD.4       | МО      | M1 M0 Timer/counter 1 mode setting.  0   0   18-bit timer/counter with 5-bit prescalar.  0   1   16-bit timer/counter.                                                                                                                                                                                        |                |                        |                             |              |                       |             |        |  |

| TMOD.5       | M1      |                                                                                                                                                                                                                                                                                                               | $-\frac{0}{1}$ |                        | nter 1 ope                  |              |                       | ding.       |        |  |

| TMOD.6       | СЛ ·    | 1   1   Timer/counter 1 operation stopped.  Timer/counter 1 count clock designation control bit.  XTAL 2 divided by 12 clocks is the input applied to timer/counter 1 when C/T = "0".  The external clock applied to the T1 pin is the input applied to timer/counter 1 when C/T = "1".                       |                |                        |                             |              |                       |             |        |  |

| TMOD.7       | GATE    | When this bit is "0", the TR1 bit of TCON is used to control to stop of timer/counter 1 counting.  If this bit is "1", timer/counter 1 starts counting when both to TCON and INT1 pin input signal are "1", and stops counting changed to "0".                                                                |                |                        |                             |              |                       |             | cf     |  |

## POWER CONTROL REGISTER (PCON)

| NAME         | ADDRESS | MSB<br>7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                | 5                                                    | 4                                                | 3                                                       | 2                                                                            | 1                                                      | LSE                                    |  |

|--------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------|----------------------------------------|--|

| PCON         | 87H     | SMOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | HPD                                                              | RPD                                                  | -                                                | GF1                                                     | GF0                                                                          | PD                                                     | IDL                                    |  |

| BIT LOCATION | FLAG    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                  |                                                      | FUN                                              | CTION                                                   |                                                                              |                                                        |                                        |  |

| PCON.0       | IDL .   | when IDI interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | E mode circuits, a                                               | is set, but<br>nd serial p                           | XTAL1-2, ort rema                                | timer/cou<br>in active. I                               | perations<br>nters 0, 1,<br>DLE mode<br>generated.                           | and 2, the                                             |                                        |  |

| PCON.1       | PD      | stopped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | when PD                                                          |                                                      | et. PD m                                         | ode is car                                              | erations ar<br>ncelled wh                                                    |                                                        |                                        |  |

| PCON.2       | GF0     | General purpose bit. Testing this flag when IDLE mode is cancelled by an interrupt shows whether the interrupt is a normal interrupt or an IDLE mode release interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                  |                                                      |                                                  |                                                         |                                                                              |                                                        |                                        |  |

| PCON.3       | GF1     | General processing the whether the second se | is flag wh                                                       | nen PD mo                                            | de is car                                        | ncelled by                                              | an interru<br>PD mode r                                                      | pt shows<br>elease int                                 | errupt                                 |  |

| PCON.4       | - //    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit. The                                                         | output data                                          | a is "1" if t                                    | he bit is re                                            | ead.                                                                         |                                                        |                                        |  |

| PCON.5       | RPD     | interrupt<br>if interrup<br>"0". If the i<br>bit is "1" (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | signal. Po<br>t is not en<br>nterrupt f<br>even if intess of the | wer down<br>habled by<br>lag is set t<br>errupt is d | mode ca<br>E (interno<br>o "1" by a<br>isabled), | annot be out<br>upt enable<br>in interrup<br>the progra | lown mode<br>cancelled to<br>register)<br>trequests<br>am is execustruction. | by interrupt<br>when this<br>signal when<br>suted from | ot signa<br>bit is<br>en this<br>n the |  |

|              |         | ENABL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | E                                                                | RECOVER                                              | $\neg$                                           |                                                         |                                                                              |                                                        |                                        |  |

|              |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  | 0                                                    | PWDr                                             | not cancelled                                           | 1                                                                            |                                                        |                                        |  |

|              |         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  | 0                                                    | Execut                                           | e interrupt r                                           | outine                                                                       |                                                        |                                        |  |

| •            |         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                  | 1                                                    |                                                  | e next addre                                            |                                                                              |                                                        |                                        |  |

|              |         | 1 -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                  | 1                                                    |                                                  | e interrupt re                                          |                                                                              |                                                        |                                        |  |

| PCON.6       | HPD     | The hard power down setting mode is enabled when this bit is set to "1" If the level of the power failure detect signal applied to the HPD1 pin (pir 3.5) is changed from "1" to "0" when this bit is "1", XTAL1-2 oscillation is stopped and the system is put into hard power down mode. HPD mode cancelled when the CPU is reset, or HPD1 pin go high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                  |                                                      |                                                  |                                                         |                                                                              |                                                        |                                        |  |

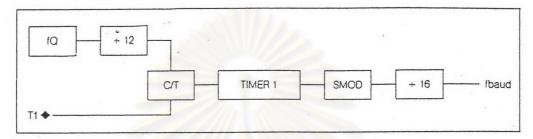

| PCON.7       | SMOD    | When the time/counter 1 carry signal is used as a clock in mode 1, 2 or 3 of the serial port, this bit has the following functions. The serial port operation clock is reduced by 1/2 when the bit is "0" for delayed processing. And when the bit is "1", the serial port operation clock is normal for faster processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                  |                                                      |                                                  |                                                         |                                                                              |                                                        |                                        |  |

| 8 | 3 | C | 15 | 4 |

|---|---|---|----|---|

|   | • | ~ | -  | 7 |

## TIMER CONTROL REGISTER (TCON)

| NAME         | ADDRESS | MSB<br>7            | 6                                                                                                                                                        | 5           | 4                                           | 3             | 2                 | 1          | LSE  |  |  |  |

|--------------|---------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------|---------------|-------------------|------------|------|--|--|--|

| TCON         | 88H     | TF1                 | TR1                                                                                                                                                      | TFO         | TRO                                         | IE1           | IT1               | IE0        | ПО   |  |  |  |