#### CHAPTER 3

#### MATHEMATICAL ANALYSIS OF SWITCHING REGULATOR

## 3.1 Introduction

An analysis of a switching regulator system is introduced in this chapter. A ¶-type filter circuit is used as a RF Noise Filter in the regulator system. The mathematical analysis of the switching regulator system will be performed for easy referred in the following chapters. In addition, the switching losses due to all conductions, switching in power transistors, driver circuits and transformer losses are also presented.

## 3.2 RF Noise Filter

In the high speed switching operation, the interference voltage at the line input voltage due to noise is the major problem. Using Fouries analysis, the harmonics at higher frequencies will be reduced, but in the switching system the harmonics do not obey this rule. Tunnbull 13 observed that the anomolous magnitudes of these harmonics occur during the frequency ranges of 1 MHz to 10 MHz. Recently, John Turnbull has discussed this phenomena and also suggested some techniques to reduce these anomolous voltages. Consequently, this difficulty may be overcome by using a RF Noise Filter which will be designed and used in this research.

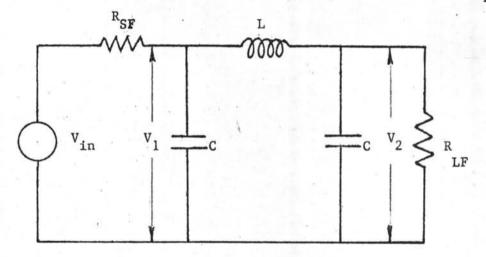

In practice, low pass filters are considered to attenuate any particular interference frequency and their transmission losses can be determined. A 1-type filter circuit is used here and shown in Fig 3.1.

Fig 3.1 A ¶-type filter circuit

For maximum power transfer condition, the load impedance  $R_{LF}$  must be equal to the source impedance  $R_{SF}$ , therefore the output voltage,  $V_2$ , can be expressed as

$$V_{2} = \frac{V_{in}}{2-2\omega^{2}LC+j\left[\frac{\omega L}{R_{LF}} + 2R_{LF}\omega C-\omega^{3}R_{LF}C^{2}L\right]}$$

(3.1)

From Fig. 3.1, the  $\P$ -type filter circuit may be considered as a no loss filter, then the input voltage,  $Y_{in}$  becomes

$$V_{in} = 2V_1 \tag{3.2}$$

Consequently, the ratio of the square of the absolute magnitude voltage between  $\mathbf{V}_1$  and  $\mathbf{V}_2$  is written as

$$\left| \frac{v_1}{v_2} \right|^2 = 1 + \omega^2 \left( \frac{L^2}{2} + c^2 R_{LF}^2 - LC \right) + \omega^4 \left( \frac{L^2 C^2}{2} - LR_{LF}^2 C^3 \right)$$

$$+ \omega \frac{^{6}R_{LF}^{2}L^{2}C}{^{4}}$$

(3.3)

and the power loss in dB may be obtained as

$$P_f = 10 \log_{10} \left| \frac{v_1}{v_2} \right|^2$$

(3.4)

It can be seen that this power loss will be zero when the output voltage  $\mathbf{V}_2$  is equal to  $\mathbf{V}_1$

Since the ratio of  $\frac{V}{V_2}$  at the cut-off frequency,  $f_0$  is  $\sqrt{2}$ , then the ratio of the square of the absolute magnitude voltages in eqn.(3.3) becomes.

$$1 + \omega_{o}^{2} \left(\frac{L^{2}}{4R_{LF}^{2}} + C^{2}R_{LF}^{2} - LC\right) + \omega_{o}^{4} \left(\frac{L^{2}C^{2}}{2!} - LR_{LF}^{2}C^{3}\right) + \omega_{o}^{6}R_{LF}^{2}L^{2}C^{4}$$

$$= 2 \qquad (3.5)$$

From the above equation, it is seen that the term  $\frac{\omega_0^6 R_{LF}^2 L^2 C^4}{\sqrt{4}}$  is very greater than  $\omega_0^2 (\frac{L^2}{4R_{LF}^2} + C^2 R_{LF}^2 - LC)$  and  $\omega_0^4 (\frac{L^2 C^2}{2} - LR_{LF}^2 C^3)$ . Hence the value of the frequency  $\omega_0$  can be approximately calculated by

$$\omega_{o} = \left[\frac{2}{R_{LF}LC^{2}}\right]^{1/3} \tag{3.6}$$

From the equation (3.4), the power loss  $P_f$  can be expressed in terms of the damping ratio, d and the frequency as

$$P_{f} = 10 \log_{10} \left[ 1 + \frac{\omega_{o}^{2}}{\omega_{o}^{2}} (\frac{1}{d} 1/3 - d^{2/3})^{2} - \frac{2\omega^{4}}{\omega_{o}^{4}} (\frac{1}{d} 1/3 - d^{2/3}) + \frac{\omega^{6}}{\omega_{o}^{6}} \right]$$

(3.7)

Where d is the damping ratio, and

$$d = \frac{-L}{2CR_{LF}^2}$$

(3.8)

In general, the design engineers will first choose the cut-off frequency f and the value of the damping ratio d then the appropriate values of L, C can be determined from eqns.(3.6) and(3.7). A typical example for determining these values of L, C in the 1 -type filter will be given in chapter 5.

## 3.3 Mathematical analysis

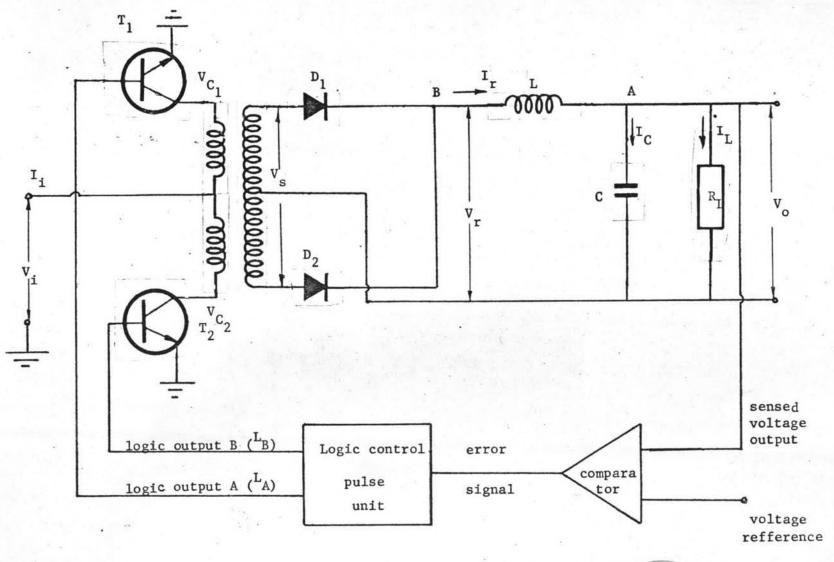

The mathematical analysis of the switching regulator system shown in Fig 3.2 is based on the following assumptions.

- (a) During each operation cycle, T, the voltage across the choke L is assumed to be constant.

- (b) The saturation voltage of transistors,  $T_1$  and  $T_2$  and the conduction voltage of the diodes,  $D_1$  and  $D_2$  are assumed to be zero for the analysis.

- (c) The rise time, fall time and delay time of the voltage waveform in the system are neglected.

- (d) The choke L is assumed to be lossless.

- (e) The transformer loss is also neglected.

Consider a switching system shown in Fig. 3.2

Let  $V_i$  be the input voltage

$v_o$  be the output voltage 002437

I, be the input current

I, be the output current

Fig. 3.2 A switching regulator system

V pp be the output ripple voltage I<sub>CT1</sub> be the average collector current of transistor T, I<sub>CT2</sub> be the average collector current of transistor  $T_2$ v<sub>r</sub> be the secondary voltage at point B be the number of turn ratio n:1 of transformer be the choke current f be the operating frequency of a switching power transistor Eo be the output voltage at which transistor turn on Ic be the capacitor current be the voltage on capacitor(at  $t = 0, V_C = E_0$ )

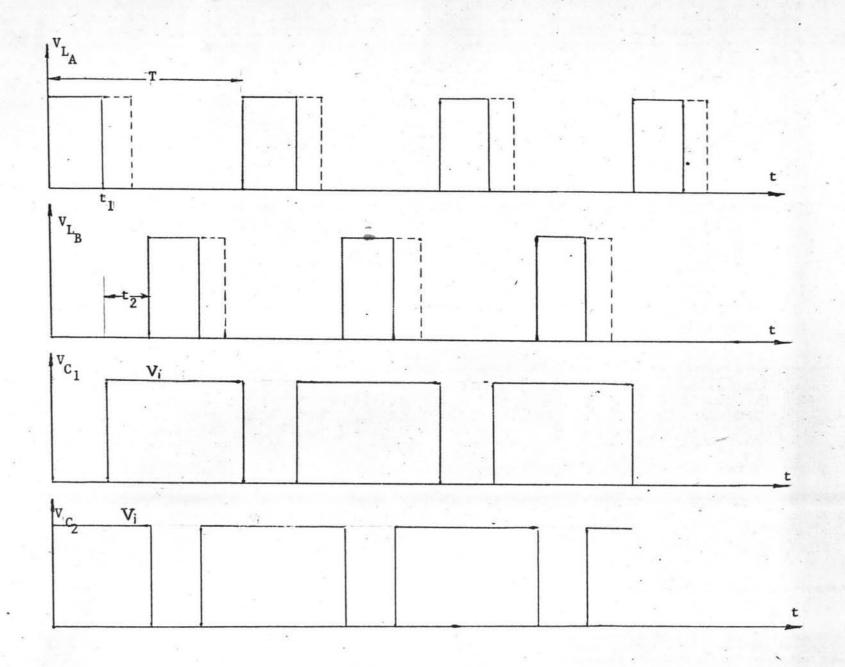

From Fig.3.2, after comparing the voltage output and the refference voltage, the duration of the logic pulse will be controled by the error signal. The dc input voltage  $V_i$  is chopped by transistors  $T_1$  and  $T_2$  controlled by the logic control pulse unit. The waveform of the voltages at  $L_A$ ,  $L_B$  and collector voltage of transistors can be illustrated in Fig.3.3

At steady state condition, let the output voltage be  $V_0$  and the pulse width produced by the logic control pulse unit be  $t_1$  as indicated in Fig.3.3

Hence, the average input current, I may be determined by integration the current waveform.

Fig. 3.3 The voltage waveforms at the output of the control pulse unit,  $L_A$ ,  $L_B$  and the collector voltage ,  $v_{C_1}$ ,  $v_{C_2}$

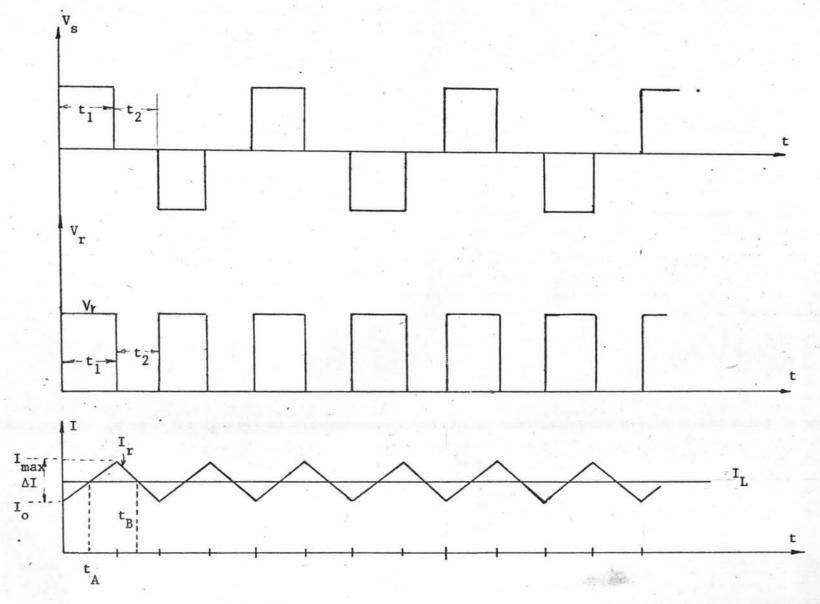

Fig. 3.4 The waveform of voltage and current at various points of the system shown in Fig. 3.2

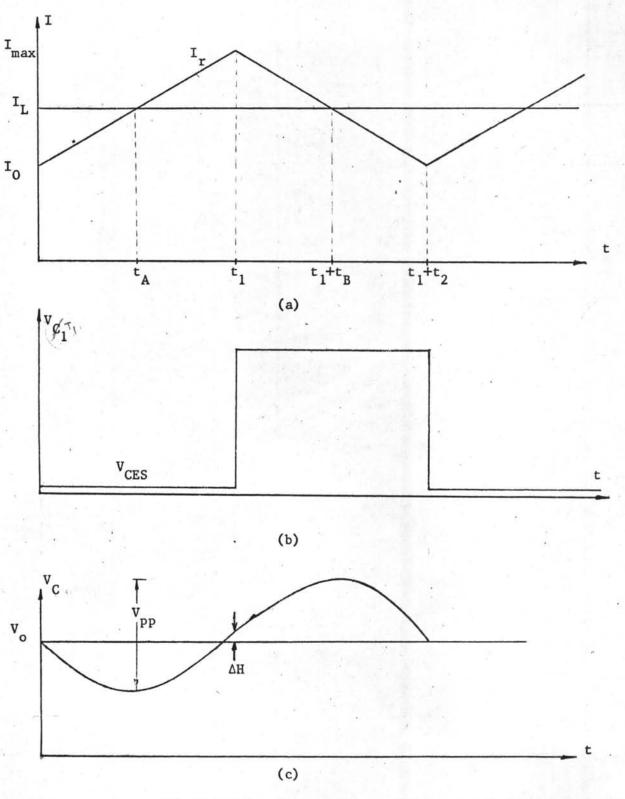

Fig.3.5 (a) The waveform of the current delivered to load

- (b) The collector voltage of the transistor  $T_1$

- (c) The output ripple voltage waveform

$$I_{av} = \frac{1}{T} \int_{0}^{T} I_{i} dt$$

$$= \frac{1}{T} \int_{0}^{t_{1}} \frac{E_{i}}{n^{2}R_{L}} dt + \frac{1}{T} \int_{1+t_{2}}^{2t_{1}+t_{2}} \frac{E_{i}}{n^{2}R_{L}} dt$$

$$= \frac{2E_{i}t_{1}}{Tn^{2}R_{T}}$$

(3.9)

Where  $t_1$  be the time corresponding to the pulse width produced by the logic control pulse unit.

$\mathbf{t}_2$  be the time corresponding to the off duty produced by the logic control pulse unit.

Similarly, the average collector currents of the transistors  $\mathbf{T}_1$  and  $\mathbf{T}_2$  are

$$I_{CT_1} = \frac{1}{T} \int_{0}^{T} I_{CT_1} dt$$

$$= \frac{V_i t_1}{Tn^2 R_L}$$

$$I_{CT_2} = \frac{1}{T} \int_{0}^{T} I_{CT_2} dt$$

$$= \frac{V_i t_1}{Tn^2 R_L}$$

$$= \frac{V_i t_1}{Tn^2 R_L}$$

(3.10)

It can be seen that the average collector current in both eqns.

(3.10) and (3.11) are the same.

In the secondary side of the transformer shown in the Fig. 3.2 , the current I during the time 0 < t < t  $_1$  can be expressed as

$$I_r = \frac{(v_r - v_o)}{L} + I_o$$

(3.12)

Hence, the energy per cycle at the secondary transformer is determined by

$$P_{C} = 2 \int_{0}^{t_{1}} V_{r} I_{r} dt$$

$$= \frac{V_{r} (V_{r} - V_{o}) t_{1}^{2}}{L} + 2 V_{r} I_{o} t_{1}$$

(3.13)

According to the previous assumptions(b)and(d), the energy per cycle PC divided by T will be the average power output of the system.

From Fig3.2 and eqn(3.12), the maximum current in diodes can be expressed as

$$I_{\text{max}} = \frac{(V_r - V_o)}{L} t_1 + I_o$$

(3.14)

From eqns. (3.13) and (3.14), the energy per cycle becomes

$$P_{C} = \frac{V_{r}L(I_{max}^{2} - I_{o}^{2})}{V_{r} - V_{o}}$$

From Fig. 3.3 , the current  $I_r$  along the choke during the time  $t_1 < t < t_1 + t_2$  can be expressed as

$$I_r = I_{max} - \frac{V_o(t-t_1)}{I_c}$$

(3.16)

When the time  $t = t_1 + t_2$ , the current  $I_r$  is then equal to  $I_o$ . Therefore, the time  $t_2$  will be

$$t_2 = \frac{L^{(I_{max}-I_o)}}{V_o}$$

(3.17)

From Fig. 3.3 the operating frequency of power transistors is

$$f = \frac{1}{2(t_1 + t_2)}$$

(3.18)

From eqns.(3.14),(3.17) and(3.18), the value of the choke,L,can be expressed as

$$L = \frac{V_{o}(V_{r}-V_{o})}{2V_{r}f(I_{max}-I_{o})}$$

(3.19)

From Fig. 3.4, it can be seen that the time  $t_A$  is the time when the value of  $I_r$  reaches  $I_L$ , for 0  $^< t_A^< t_1$ , and the time  $t_B$  is the time when the value of  $I_r$  decays to  $I_L$ , for  $t_1^< t_B^< t_1^+ t_2^-$

Hence, from eqns. (3.12) and (3.16) the value of  $t_{A}$ ,  $t_{B}$  can be expressed as

$$t_{A} = \frac{(I_{L} - I_{o})}{V_{r} - V_{o}}$$

(3.20)

$$t_{B} = \frac{I_{\text{max}} - I_{L} L}{V_{Q}}$$

(3.21)

respectively,

The ripple peak to peak voltage may be expressed as

$$V_{pp} = V_{Cmax} - V_{Cmin}$$

(3.22)

where

$V_{\rm pp}$  is the peak to peak ripple voltage

$V_{Cmax}$  is the upper ripple voltage

$V_{\mbox{Cmin}}$  is the lower ripple voltage

From Fig. 3.5 let

E be the output voltage at which transistor turns on.

$E_0 + \Delta H$  be the output voltage at which transistor turns off. From Fig 3.2, and applying Kirchoff's current law at node A, the current  $I_C$  along the capacitor during the time  $0 < t < t_1$  is

$$I_C = -I_L + (\underline{v_r - v_o}) t + I_o$$

(3.23)

Therefore, the value of voltage across the capacitor during the

time

$$0 < t < t_1^{is}$$

$V_C(t) = E_o - \frac{(I_L - I_o)t}{C} + \frac{(V_r - V_o)t^2}{2LC}$

(3.24)

From Fig. 3.5, the minimum value of  $V_C(t)$  occurs when  $t = t_A$  thus, we obtain

$$V_{Cmin}(t_A) = E_o - \frac{(I_L - I_o)^2 L}{2C (V_r - V_o)}$$

(3.25)

When  $t = t_1$ , the capacitor voltage becomes

$$v_{c}(t_{1}) = E_{o} - \frac{(I_{c} - I_{o})}{c} t_{1} + \frac{(v_{r} - v_{o})}{2LC} t_{1}^{2}$$

(3.26)

From eqns. (3.12) and (3.16), the different current  $\Delta I$  in these equations can be expressed as

$$\Delta I = \frac{(v_r - v_o)}{L} t_1^{-1} = \frac{v_o t_2}{L}$$

(3.27)

From eqns (3.18) and (3.27) the time t, becomes

$$t_1 = \frac{v_0}{2fV_r} \tag{3.28}$$

From Fig. 3.5, substituting the value of  $t_1$  into eqn.(3.26), then the different voltage between  $V_C(t_1)$  and  $E_0$ ,  $\Delta H$  will be

$$\Delta H = (V_r - V_o) \left[ \frac{V_o}{2fV_r} \right]^2 \frac{1}{2LC} - \frac{(I_L - I_o)}{2fCV_r} V_o$$

(3.29)

Similarly, from Fig. 3.2 and applying Kirchoff's current law at node A, the current  $I_C$  along the capacitor during the time  $t_1 < t < t_1 + t_2$  is

$$I_{C} = -I_{L} + I_{max} - \frac{V_{o}(t - t_{1})}{L}$$

(3.30)

Therefore, the voltage across the capacity during the time

$t_1 < t < t_1 + t_2$  is

$$V_{C}(t) = E_{o} + \Delta H + \frac{(I_{max} - I_{L})(t - t_{1})}{C} - \frac{V_{o}(t - t_{1})^{2}}{2LC}$$

(3.31)

Thus, we obtain

$$V_{\text{Cmax}}(t + t_B) = E_0 + \Delta H + \frac{(I_{\text{max}} - I_L)^2 L}{2CV_0}$$

(3.32)

The peak to peak ripple voltage Vpp can be determined by

$$v_{pp} = v_{Cmax}(t_1 + t_B) - v_{Cmin}(t_A)$$

$$= \Delta H + \frac{LV_r (I_{max} - I_L)^2}{2CV_o (V_r - V_o)}$$

(3.33)

Substituting the value of  $\Delta H$  into eqn (3.33) then the peak to peak ripple voltage  $V_{np}$  will be

$$\frac{v_{pp}}{v_{pp}} = \frac{v_r - v_o}{2LC} \left[ \frac{v_o}{2fv_r} \right]^2 - \frac{(I_L - I_o) v_o}{2fcv_r} + \frac{Lv_r (I_{max} - I_L)^2}{2cv_o (v_r - v_o)}$$

(3.34)

Therefore the ripple factor is

$$r = \frac{V}{E} pp \times 100 \tag{3.35}$$

It can be seen that this ripple factor varies with L,  $\rm V_r, \, \rm V_o, \, f,$   $\rm I_{max}, \, \rm I_L$  and C

# 3.4 Switching regulator loss

In a switching regulator system, most designers have their attention on four main types of losses.

These losses are summarized as .

- (a) Conduction loss

- (b) Switching loss

- (c) Driver loss & control circuit loss

- (d) Transformer loss

#### 3.4.1 Conduction loss

This type of losses can be divided into three parts.

#### First part

Normally, the saturation voltage of a silicon type transistor is in the value of 0.5 to 1 Volt. Therefore, the loss occurs in the transistor will be

$$P_{TL} = y_{CES} C_{T}$$

Watts (3.36)

Where V<sub>CES</sub> be a saturation voltage drop between collector and emitter. (Volt)

$I_C$  be the collector current of the transistor. (Amp.)

## .Second part

This loss occurs during the forward. The voltage drop

in a silicon diode is about 0.6 to 1 Volt. Therefore the power loss can

be obtained by

$$P_{DL} = V_d I_d \frac{t_1}{T} \text{ Watts}$$

(3.37)

Where  $V_d$  be the forward voltage drop across the diode.  $I_d$  be the forward current in diode.

## Third part

This loss occurs due to the resistance of the winding and normally is expressed in term of a factor of merit Q. In this case, the power loss can be determined by

$$P_{LL} = \frac{Q}{P_{re}} \tag{3.38}$$

Where P be the reactive loss and is obtained from

$$P_{re} = I_{Ch}^2 \times X_L \tag{3.39}$$

## 3.4.2 Switching loss

This type of loss occurs during the switching operation when transistors and diodes are used. In practice, the power loss due to this situration can be expressed in the form.

$$P_{ST} = fE_C I_C t_{off}$$

(3.40)

$$P_{SD} = fE_r I_D t_{off}$$

(3.41)

Where  $P_{cm}$  is the switching loss for transistor.

$\mathbf{E}_{\mathbf{C}}$  is a collector voltage during the transistor off.

I c is the collector current for transistor during the transistor on.

Pch is the switching loss for diode.

I, is the forward current of diode.

toff is the turn off time.

## 3.4.3 Driver loss and control unit loss

The switching transistors must be driven with a substantial amount of base current to keep the saturation voltage down. The amount of the base current varies from device to device, and a reasonable guess is to choose industrial silicon type transistors having the value of  $h_{\rm FEmin} = 10$

In this case, the approximate power loss due to the driver can be expressed as.

$$P_{DR} = \frac{I_C}{h_{FE}} \times V_{CC} \qquad (3.42)$$

For the control unit, loss the IC's which consume low current are used. Therefore this, loss is very small when compared to the driver loss.

#### 3.4.4 High frequency transformer loss

This loss may be reduced when the high grade ferrite material is used. The efficiency of this kind of transformer can be greatly improved if the proper design has been made. A typical design of a high frequency transformer including numerical results will be presented in chapter 4.